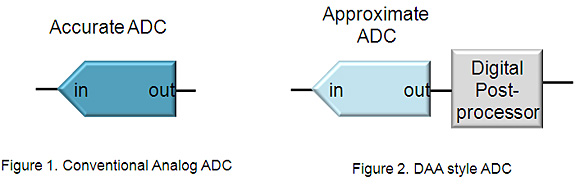

Yesterday was Cadence’s annual mixed-signal technology forum. I think that there was a definite theme running through many of the presentations, namely that wireless communication of one kind or another is on a sharp rise with more and more devices needing to connect to WiFi, Bluetooth and so on. This was most obvious during the panel session after lunch which was on the ecosystem needed for the internet of things. However, the way to design radios (and analog interfaces in general) is increasingly to design the smallest possible analog blocks and then use digital, even quite complex digital, to calibrate the analog.David Su of Qualcomm gave the opening keynote on Designing WLAN SoCs. He started with a history of wireless LANs, pointing out the huge increase of 3 orders of magnitude increase in data rates. The effect of this has been that data cost has been declining about 2X per year even though the cost of a wireless router has been roughly static. We went from 1MHz to 160MHz channels and now with future standards allowing 4 or 8 channels to be used.He is a big fan of minimizing the analog and using digital to calibrate, what he (and Cadence) calls digital assisted analog design. Of course there are still big challenges. The biggest problem, beyond simply power, is digital interference with the analog on the SoC. There are various strategies for coping with this, minimizing the aggressor (the digital logic) by techniques like clock gating and minimizing switching large registers on one clock cycle. Next, strengthen the victim (analog) by wells and robust analog design. And then try and minimize the coupling by spacing the blocks apart and even potentially some process tricks such as deep wells.Ken Kundert (who used to work at Cadence and was the principal author of Spectre) made a plea that the way that analog engineers designed needed to modernize or designing these kind of digitally trimmed analog is almost impossible. If designs are to be done in a reasonable time then the digital and analog need to be designed in parallel and the most promising way to do that is to start from a spec of the analog block and use that to produce a model and a self-checking testbench. This isn’t as hard as it seems. Digital design has huge state so verification is hard, but synthesis, place & route makes implementation fairly straighforward. Analog is the other way around, specifications are simple, there is little state, but implementation is hard. Hence the need to use models since the schematic comes too late and simulates too slowly for the digital design team.

Yesterday was Cadence’s annual mixed-signal technology forum. I think that there was a definite theme running through many of the presentations, namely that wireless communication of one kind or another is on a sharp rise with more and more devices needing to connect to WiFi, Bluetooth and so on. This was most obvious during the panel session after lunch which was on the ecosystem needed for the internet of things. However, the way to design radios (and analog interfaces in general) is increasingly to design the smallest possible analog blocks and then use digital, even quite complex digital, to calibrate the analog.David Su of Qualcomm gave the opening keynote on Designing WLAN SoCs. He started with a history of wireless LANs, pointing out the huge increase of 3 orders of magnitude increase in data rates. The effect of this has been that data cost has been declining about 2X per year even though the cost of a wireless router has been roughly static. We went from 1MHz to 160MHz channels and now with future standards allowing 4 or 8 channels to be used.He is a big fan of minimizing the analog and using digital to calibrate, what he (and Cadence) calls digital assisted analog design. Of course there are still big challenges. The biggest problem, beyond simply power, is digital interference with the analog on the SoC. There are various strategies for coping with this, minimizing the aggressor (the digital logic) by techniques like clock gating and minimizing switching large registers on one clock cycle. Next, strengthen the victim (analog) by wells and robust analog design. And then try and minimize the coupling by spacing the blocks apart and even potentially some process tricks such as deep wells.Ken Kundert (who used to work at Cadence and was the principal author of Spectre) made a plea that the way that analog engineers designed needed to modernize or designing these kind of digitally trimmed analog is almost impossible. If designs are to be done in a reasonable time then the digital and analog need to be designed in parallel and the most promising way to do that is to start from a spec of the analog block and use that to produce a model and a self-checking testbench. This isn’t as hard as it seems. Digital design has huge state so verification is hard, but synthesis, place & route makes implementation fairly straighforward. Analog is the other way around, specifications are simple, there is little state, but implementation is hard. Hence the need to use models since the schematic comes too late and simulates too slowly for the digital design team. Wilbur Luo of Cadence gave an overview of the mixed signal offering. Increasingly the methodology revolves around having Virtuoso and Encounter Digital Implementation (EDI) running on a common open access database able to share the same semantics without losing things like constraints in implementation. There are even lower capacity versions of Encounter, Tempus, Voltus etc which run inside Virtuoso to enable digital design.After lunch there was a panel with Rob Consaro of Freeescale, Ron Moore of ARM, Ian Dennison from Cadence Scotland and Doug Patulio from TSMC. Rob related a tale of how the tools and methodologies now mean that power methodology is now a solved problem compared to a few years ago when he tried and failed to design a chip with lots of power domains in the days before CPF/UPF. But noise is the big challenge going forward. Ron said in some cases ARM is going back to a single power domain to keep the area down which makes it a challenge to handle leakage.Doug pointed out that TSMC has always been in the business of helping customers get to the next node. But he feels that 28nm is the last time that will happen. Some people will move to 16FF+ of course. But TSMC is putting a lot of effort into re-engineering older processes using what they have learned from the advanced processes, especially for ultra-low power aimed specifically at IoT. Ian talked about putting sensors and analog and digital all on the same die, perhaps using TSVs or other 3D technologies. There is a mismatch at present as to which process sensors and other MEMS devices need for fabrication, with which digital technologies make most sense. One question from the audience asked about software: how do we get analog models running on emulators so that we can use virtual platform technology to do early software development? There is some possibility that using real-number models will help but there was no clear answer.Oh, and I won a copy of the Mixed-signal Methodology Guide.

Wilbur Luo of Cadence gave an overview of the mixed signal offering. Increasingly the methodology revolves around having Virtuoso and Encounter Digital Implementation (EDI) running on a common open access database able to share the same semantics without losing things like constraints in implementation. There are even lower capacity versions of Encounter, Tempus, Voltus etc which run inside Virtuoso to enable digital design.After lunch there was a panel with Rob Consaro of Freeescale, Ron Moore of ARM, Ian Dennison from Cadence Scotland and Doug Patulio from TSMC. Rob related a tale of how the tools and methodologies now mean that power methodology is now a solved problem compared to a few years ago when he tried and failed to design a chip with lots of power domains in the days before CPF/UPF. But noise is the big challenge going forward. Ron said in some cases ARM is going back to a single power domain to keep the area down which makes it a challenge to handle leakage.Doug pointed out that TSMC has always been in the business of helping customers get to the next node. But he feels that 28nm is the last time that will happen. Some people will move to 16FF+ of course. But TSMC is putting a lot of effort into re-engineering older processes using what they have learned from the advanced processes, especially for ultra-low power aimed specifically at IoT. Ian talked about putting sensors and analog and digital all on the same die, perhaps using TSVs or other 3D technologies. There is a mismatch at present as to which process sensors and other MEMS devices need for fabrication, with which digital technologies make most sense. One question from the audience asked about software: how do we get analog models running on emulators so that we can use virtual platform technology to do early software development? There is some possibility that using real-number models will help but there was no clear answer.Oh, and I won a copy of the Mixed-signal Methodology Guide.

More articles by Paul McLellan…

Instance

Array

(

[node_name] => Cadence

[node_id] => Array

(

[0] => 2

)

)

Instance

Array

(

[node_name] =>

[node_id] => Array

(

[0] => 2

)

[title] => Recent Forum Threads

)

Threads

XF\Mvc\Entity\ArrayCollection Object

(

[entities:protected] => Array

(

[24895] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 57

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24895

[node_id] => 2

[title] => Samsung Is Unfazed by the DRAM Crash Hysteria, Raises Prices by 30% for Q2 After Doubling Them in Q1

[reply_count] => 1

[view_count] => 59

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1775657638

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99035

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775657744

[last_post_id] => 99036

[last_post_user_id] => 5

[last_post_username] => Daniel Nenni

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5

[username] => Daniel Nenni

[username_date] => 0

[username_date_visible] => 0

[email] => dnenni@semiwiki.com

[custom_title] => Founder

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 3

[secondary_group_ids] => 4,5,132

[display_style_group_id] => 3

[permission_combination_id] => 88

[message_count] => 15465

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1280720820

[last_activity] => 1775657986

[last_summary_email_date] => 1605968657

[trophy_points] => 113

[alerts_unviewed] => 102

[alerts_unread] => 102

[avatar_date] => 1663211649

[avatar_width] => 110

[avatar_height] => 107

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 1

[is_admin] => 1

[is_banned] => 0

[reaction_score] => 9355

[warning_points] => 0

[is_staff] => 1

[secret_key] => 0HwyUVVHCwJotUUVEpvqAclfYJdGNPpw

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8507

[message_count] => 62283

[last_post_id] => 99036

[last_post_date] => 1775657744

[last_post_user_id] => 5

[last_post_username] => Daniel Nenni

[last_thread_id] => 24895

[last_thread_title] => Samsung Is Unfazed by the DRAM Crash Hysteria, Raises Prices by 30% for Q2 After Doubling Them in Q1

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24890] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 61

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24890

[node_id] => 2

[title] => Bernie Sanders has a plan to stop the AI industry

[reply_count] => 13

[view_count] => 481

[user_id] => 396

[username] => swka

[post_date] => 1775506549

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98985

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775657400

[last_post_id] => 99034

[last_post_user_id] => 38697

[last_post_username] => blueone

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 58

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 396

[username] => swka

[username_date] => 0

[username_date_visible] => 0

[email] => swka@hotmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 178

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1294249501

[last_activity] => 1775608686

[last_summary_email_date] => 1686406808

[trophy_points] => 43

[alerts_unviewed] => 8

[alerts_unread] => 8

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 154

[warning_points] => 0

[is_staff] => 0

[secret_key] => OO7IirVdCg0w0g8RomEV2hwUwfXsJgMD

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8507

[message_count] => 62283

[last_post_id] => 99036

[last_post_date] => 1775657744

[last_post_user_id] => 5

[last_post_username] => Daniel Nenni

[last_thread_id] => 24895

[last_thread_title] => Samsung Is Unfazed by the DRAM Crash Hysteria, Raises Prices by 30% for Q2 After Doubling Them in Q1

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24678] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 65

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24678

[node_id] => 2

[title] => I'm having trouble understanding Broadcom's claimed AI revenue results and projections

[reply_count] => 24

[view_count] => 3832

[user_id] => 38697

[username] => blueone

[post_date] => 1772681440

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98065

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775656907

[last_post_id] => 99033

[last_post_user_id] => 38697

[last_post_username] => blueone

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 62

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 38697

[username] => blueone

[username_date] => 0

[username_date_visible] => 0

[email] => rob8633@hotmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Denver

[visible] => 0

[activity_visible] => 0

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 2591

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1621824096

[last_activity] => 1775660976

[last_summary_email_date] =>

[trophy_points] => 113

[alerts_unviewed] => 0

[alerts_unread] => 0

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 3453

[warning_points] => 0

[is_staff] => 0

[secret_key] => aGlUsVcP2cy-QllnjVLMCtpGT8e-_F_T

[privacy_policy_accepted] => 1621824096

[terms_accepted] => 1621824096

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8507

[message_count] => 62283

[last_post_id] => 99036

[last_post_date] => 1775657744

[last_post_user_id] => 5

[last_post_username] => Daniel Nenni

[last_thread_id] => 24895

[last_thread_title] => Samsung Is Unfazed by the DRAM Crash Hysteria, Raises Prices by 30% for Q2 After Doubling Them in Q1

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24892] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 69

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24892

[node_id] => 2

[title] => "Intel is proud to join the Terafab project with @SpaceX, @xAI, and @Tesla to help refactor silicon fab technology"

[reply_count] => 14

[view_count] => 1644

[user_id] => 90385

[username] => NY_Sam2

[post_date] => 1775574772

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99001

[first_post_reaction_score] => 2

[first_post_reactions] => {"1":2}

[last_post_date] => 1775656335

[last_post_id] => 99032

[last_post_user_id] => 335651

[last_post_username] => DanX

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 66

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 90385

[username] => NY_Sam2

[username_date] => 0

[username_date_visible] => 0

[email] => petekennedy1989@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/New_York

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 38

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1642621712

[last_activity] => 1775574791

[last_summary_email_date] => 1767709207

[trophy_points] => 18

[alerts_unviewed] => 19

[alerts_unread] => 19

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 57

[warning_points] => 0

[is_staff] => 0

[secret_key] => egi-LmWHpsbQRZ7Y0Lk56hMyhUsrDhDE

[privacy_policy_accepted] => 1642621712

[terms_accepted] => 1642621712

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8507

[message_count] => 62283

[last_post_id] => 99036

[last_post_date] => 1775657744

[last_post_user_id] => 5

[last_post_username] => Daniel Nenni

[last_thread_id] => 24895

[last_thread_title] => Samsung Is Unfazed by the DRAM Crash Hysteria, Raises Prices by 30% for Q2 After Doubling Them in Q1

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24889] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 73

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24889

[node_id] => 2

[title] => The Quantum Foundry: Google Including Neutral Atom Qubit Approach

[reply_count] => 3

[view_count] => 330

[user_id] => 19450

[username] => user nl

[post_date] => 1775454771

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98968

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775650697

[last_post_id] => 99026

[last_post_user_id] => 20231

[last_post_username] => Barnsley

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 19450

[username] => user nl

[username_date] => 0

[username_date_visible] => 0

[email] => mauricehmjanssen@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 1

[style_variation] =>

[timezone] => Europe/Amsterdam

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 539

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1424291496

[last_activity] => 1775659819

[last_summary_email_date] =>

[trophy_points] => 63

[alerts_unviewed] => 0

[alerts_unread] => 1

[avatar_date] => 1726169369

[avatar_width] => 384

[avatar_height] => 384

[avatar_highdpi] => 1

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 392

[warning_points] => 0

[is_staff] => 0

[secret_key] => V-1lb5_AW69yhzqA5ok9b64U0fMjJiqf

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8507

[message_count] => 62283

[last_post_id] => 99036

[last_post_date] => 1775657744

[last_post_user_id] => 5

[last_post_username] => Daniel Nenni

[last_thread_id] => 24895

[last_thread_title] => Samsung Is Unfazed by the DRAM Crash Hysteria, Raises Prices by 30% for Q2 After Doubling Them in Q1

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24868] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 77

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24868

[node_id] => 2

[title] => Intel to Repurchase 49% Equity Interest in Ireland Fab Joint Venture

[reply_count] => 33

[view_count] => 3705

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1775054550

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98833

[first_post_reaction_score] => 1

[first_post_reactions] => {"1":1}

[last_post_date] => 1775593099

[last_post_id] => 99013

[last_post_user_id] => 14042

[last_post_username] => hist78

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5

[username] => Daniel Nenni

[username_date] => 0

[username_date_visible] => 0

[email] => dnenni@semiwiki.com

[custom_title] => Founder

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 3

[secondary_group_ids] => 4,5,132

[display_style_group_id] => 3

[permission_combination_id] => 88

[message_count] => 15465

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1280720820

[last_activity] => 1775657986

[last_summary_email_date] => 1605968657

[trophy_points] => 113

[alerts_unviewed] => 102

[alerts_unread] => 102

[avatar_date] => 1663211649

[avatar_width] => 110

[avatar_height] => 107

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 1

[is_admin] => 1

[is_banned] => 0

[reaction_score] => 9355

[warning_points] => 0

[is_staff] => 1

[secret_key] => 0HwyUVVHCwJotUUVEpvqAclfYJdGNPpw

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8507

[message_count] => 62283

[last_post_id] => 99036

[last_post_date] => 1775657744

[last_post_user_id] => 5

[last_post_username] => Daniel Nenni

[last_thread_id] => 24895

[last_thread_title] => Samsung Is Unfazed by the DRAM Crash Hysteria, Raises Prices by 30% for Q2 After Doubling Them in Q1

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24881] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 81

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24881

[node_id] => 2

[title] => Samsung and SK are expanding fast, but why is memory still in short supply?

[reply_count] => 19

[view_count] => 1491

[user_id] => 5185

[username] => Fred Chen

[post_date] => 1775280977

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98907

[first_post_reaction_score] => 1

[first_post_reactions] => {"1":1}

[last_post_date] => 1775587101

[last_post_id] => 99010

[last_post_user_id] => 16950

[last_post_username] => benb

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 78

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5185

[username] => Fred Chen

[username_date] => 0

[username_date_visible] => 0

[email] => chen.t.fred@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 4

[secondary_group_ids] =>

[display_style_group_id] => 4

[permission_combination_id] => 92

[message_count] => 2599

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1333032401

[last_activity] => 1775648368

[last_summary_email_date] => 1605940563

[trophy_points] => 113

[alerts_unviewed] => 0

[alerts_unread] => 0

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 1890

[warning_points] => 0

[is_staff] => 0

[secret_key] => 5m-bZq0HRSi9VA-96QONHJeevdQas5S8

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8507

[message_count] => 62283

[last_post_id] => 99036

[last_post_date] => 1775657744

[last_post_user_id] => 5

[last_post_username] => Daniel Nenni

[last_thread_id] => 24895

[last_thread_title] => Samsung Is Unfazed by the DRAM Crash Hysteria, Raises Prices by 30% for Q2 After Doubling Them in Q1

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24894] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 85

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24894

[node_id] => 2

[title] => Why Advanced Packaging Programs Fail Late: The “Reality Gap” and the Case for SEGA™

By Dr. Moh Kolbehdari

[reply_count] => 1

[view_count] => 185

[user_id] => 444140

[username] => moh.kolb

[post_date] => 1775584084

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99008

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775584121

[last_post_id] => 99009

[last_post_user_id] => 444140

[last_post_username] => moh.kolb

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 82

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 444140

[username] => moh.kolb

[username_date] => 0

[username_date_visible] => 0

[email] => moh@kolbehdari.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Phoenix

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 8

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1775069311

[last_activity] => 1775588117

[last_summary_email_date] => 1775069311

[trophy_points] => 3

[alerts_unviewed] => 3

[alerts_unread] => 3

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 1

[warning_points] => 0

[is_staff] => 0

[secret_key] => EG539H6nqaiPLLZ4UXYEvAY-Py_6iJOA

[privacy_policy_accepted] => 1775069311

[terms_accepted] => 1775069311

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8507

[message_count] => 62283

[last_post_id] => 99036

[last_post_date] => 1775657744

[last_post_user_id] => 5

[last_post_username] => Daniel Nenni

[last_thread_id] => 24895

[last_thread_title] => Samsung Is Unfazed by the DRAM Crash Hysteria, Raises Prices by 30% for Q2 After Doubling Them in Q1

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24891] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 89

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24891

[node_id] => 2

[title] => The Ridiculously Nerdy Intel Bet That Could Rake in Billions

[reply_count] => 3

[view_count] => 644

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1775518030

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98989

[first_post_reaction_score] => 4

[first_post_reactions] => {"1":4}

[last_post_date] => 1775572017

[last_post_id] => 98997

[last_post_user_id] => 1305

[last_post_username] => KevinK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5

[username] => Daniel Nenni

[username_date] => 0

[username_date_visible] => 0

[email] => dnenni@semiwiki.com

[custom_title] => Founder

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 3

[secondary_group_ids] => 4,5,132

[display_style_group_id] => 3

[permission_combination_id] => 88

[message_count] => 15465

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1280720820

[last_activity] => 1775657986

[last_summary_email_date] => 1605968657

[trophy_points] => 113

[alerts_unviewed] => 102

[alerts_unread] => 102

[avatar_date] => 1663211649

[avatar_width] => 110

[avatar_height] => 107

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 1

[is_admin] => 1

[is_banned] => 0

[reaction_score] => 9355

[warning_points] => 0

[is_staff] => 1

[secret_key] => 0HwyUVVHCwJotUUVEpvqAclfYJdGNPpw

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8507

[message_count] => 62283

[last_post_id] => 99036

[last_post_date] => 1775657744

[last_post_user_id] => 5

[last_post_username] => Daniel Nenni

[last_thread_id] => 24895

[last_thread_title] => Samsung Is Unfazed by the DRAM Crash Hysteria, Raises Prices by 30% for Q2 After Doubling Them in Q1

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24885] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 93

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24885

[node_id] => 2

[title] => Intel CEO embraces its 18A node for external customers as 18A-P gets 'inbound interest' — company cites increasing yields

[reply_count] => 11

[view_count] => 1570

[user_id] => 5185

[username] => Fred Chen

[post_date] => 1775354521

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98939

[first_post_reaction_score] => 2

[first_post_reactions] => {"1":2}

[last_post_date] => 1775566022

[last_post_id] => 98995

[last_post_user_id] => 5185

[last_post_username] => Fred Chen

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 78

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5185

[username] => Fred Chen

[username_date] => 0

[username_date_visible] => 0

[email] => chen.t.fred@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 4

[secondary_group_ids] =>

[display_style_group_id] => 4

[permission_combination_id] => 92

[message_count] => 2599

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1333032401

[last_activity] => 1775648368

[last_summary_email_date] => 1605940563

[trophy_points] => 113

[alerts_unviewed] => 0

[alerts_unread] => 0

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 1890

[warning_points] => 0

[is_staff] => 0

[secret_key] => 5m-bZq0HRSi9VA-96QONHJeevdQas5S8

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8507

[message_count] => 62283

[last_post_id] => 99036

[last_post_date] => 1775657744

[last_post_user_id] => 5

[last_post_username] => Daniel Nenni

[last_thread_id] => 24895

[last_thread_title] => Samsung Is Unfazed by the DRAM Crash Hysteria, Raises Prices by 30% for Q2 After Doubling Them in Q1

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(