Clock domain crossing (CDC) analysis is unavoidable in any modern SoC design and is challenging enough to verify in its own right. CDC plus low power management adds more excitement to your verification task. I wrote on this topic for another solution provider last year. This time I want to intro an interesting twist on the problem, revealed in a Mentor/Cypress white paper presented at DVCon San Jose last year.

Scoping down CDC analysis reduces noise, so Mentor and Cypress focused their attention on interactions between low power and CDC. Obvious candidates are around isolation management and retention registers. Since they’re working with RTL design which does not yet have power management implemented, they read the current UPF (power management constraints) together with the RTL.

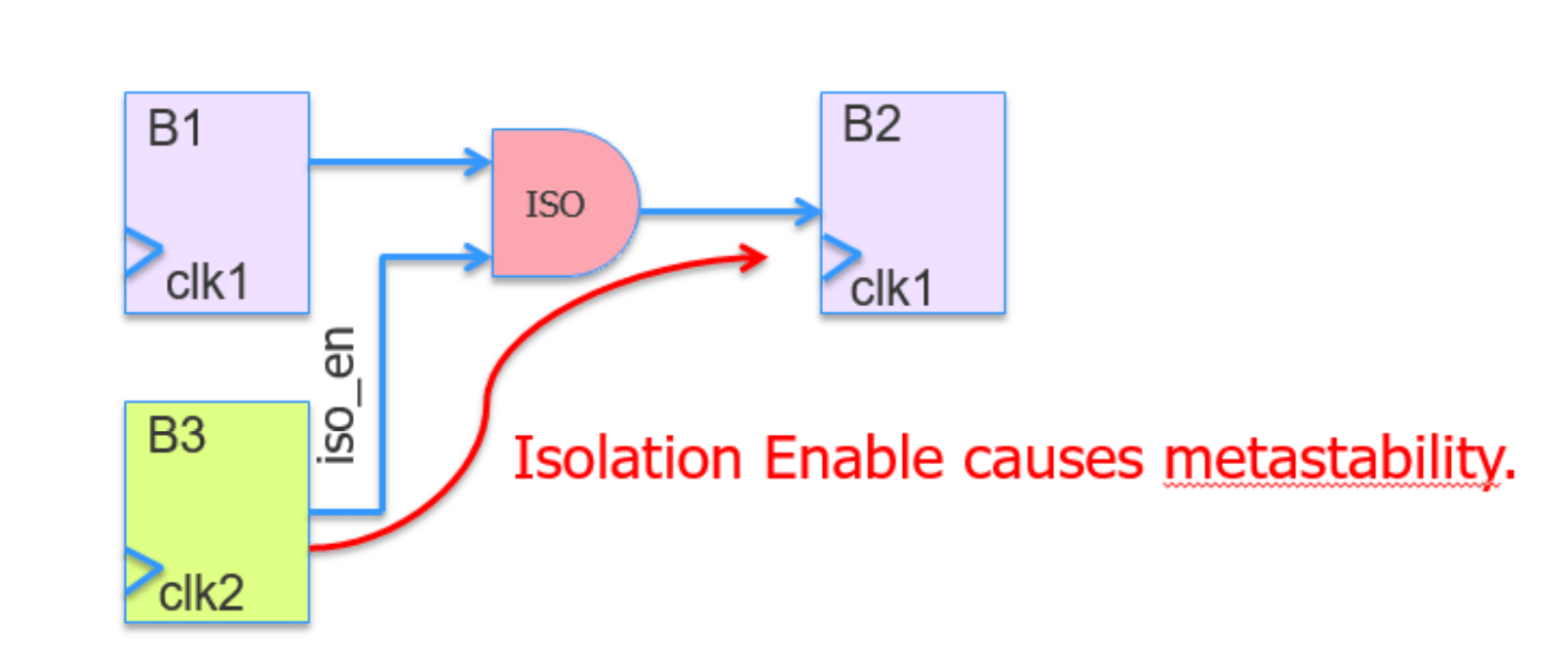

CDC and isolation control

One obvious CDC+low power problem, illustrated in the figure, would not necessarily be obvious in a CDC analysis of the RTL alone where the isolation signal is not yet connected. In this case there is a clock domain crossing between clk2 and clk1, which could lead to metastability in the B2 register when isolation is enabled (or, I think, when it is disabled). Which means you must harden B2 for metastability, or you must synchronize the isolation enable signal. Either way this is a realization that only becomes apparent when you look at the RTL and the UPF together.

CDC and retention

Retention registers provide another tricky example. In RTL a register is just a register – no power considerations of any kind. If you power off the block containing the register, the register powers off along with everything else in the block. But that can introduce a lot of latency and rework when you want to power back on. When your phone automatically powers down and a little later you start it up again, you don’t want to have to restart all your apps and re-find the last things you were looking at. You expect the phone to jump right back to where you left off. Retention registers play a role here. These registers hang on to their last state, even when you power down the domain around them. Not every register has to be retention, just enough to allow jumping back quickly to the last state when power is restored. To my knowledge, this typically works by saving state to a separate part of a special register, where that separate part sits in an always-on power domain. When you’re ready to restore, you copy that saved state back to the main register.

The CDC challenge again starts with the fact that designer flag these decisions in the UPF, not in the RTL. And choose signals to trigger state restoration which must be synchronized to the register clock. This is another case where a check has to look both at the RTL and the UPF. First to find the retention candidates and then to ensure that no restore signal has a CDC issue with its target register.

Mentor solution

Interesting stuff. I wonder if at some point we will be seeing white papers on CDC and security verification. Or maybe CDC and low power and security! You can access the Mentor white paper HERE.

Also Read:

Multicore System-on-Chip (SoC) – Now What?

A Fast Checking Methodology for Power/Ground Shorts

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.