There is an adage that says that quality is not something that can be slapped on at the end of the design or manufacturing process. Ensuring quality requires careful thought throughout development and production. Arguably this adage is more applicable to the topic of Design for Test (DFT) than almost any other area of IC development and verification. DFT is quite literally built into the design and involves every part of the chip. In addition to helping validate completed chips to ensure they meet their functional requirements, DFT is also used to feed yield and reliability statistics back into the design process to help prevent quality issues.

Detecting and preventing defects in ICs is a major area of research and technology development. Over the last 15 years DFT has been the topic of numerous academic papers and articles that rely on investigations and data derived from real world designs produced by leading semiconductor companies. To help enable these investigations and use their results to leverage DFT tool and flow development Mentor, a Siemens business, has worked with many of these companies on improved methods for DFT.

Mentor uses a partnership model for developing new and advanced features in their DFT tools. In a recent publication titled “How to Maximize Your Competitiveness in the Semiconductor Industry Using Advanced DFT” Mentor talks about how important these partnerships are and highlights some of the advances they have made possible.

One such example is how the traditional fault models dating back many years have been expanded with the cell-aware fault model that proves useful for understanding defects that can occur within cells. The Mentor publication references a jointly authored paper with AMD and ON Semiconductor that shows in detail how the cell-aware test approach can reduce defect rates.

The Mentor publication also discusses the origins of their Tessent TestKompress. Back in 2001-2002 as 130nm designs were being developed using copper interconnect it became necessary to run at-speed tests with new fault models. Mentor devised TestKompress to allow the new patterns to fit in limited tester memories. TestKompress has continued to evolve since then to help accommodate larger design sizes at smaller nodes and new test types that require more patterns. The paper cites their work with Broadcom in 2015 that resulted in an IEEE paper for DAC.

Mentor also talks about their work partnering with foundries, such as GLOBALFOUNDRIES, to improve physical failure analysis (PFA). Looking at large numbers of wafers and dies, scan diagnosis can help pinpoint defect locations and lead to understanding the failure/defect mechanisms. Scan diagnosis is used for both yield ramp and yield improvement. Mentor has also worked with fabless semiconductor companies, foundries and integrated device manufacturers to develop root-cause deconvolution (RCD) which uses AI algorithms to estimate the defect Pareto from volume diagnosis results in the presence of noise.

Another significant advancement that has been presented in an IEEE paper is Mentor’s hierarchical DFT. Performing DFT on smaller blocks individually and then wrapping them so each instance can be tested in-situ makes the processes much more manageable. Mentor mentions how both Amazon and Samsung benefited from hierarchical DFT because of improvements in runtime, pattern count and compute resources. Hierarchical DFT is so compelling that it has become the standard practice.

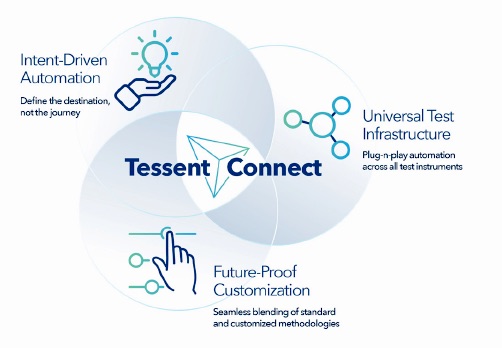

The Mentor paper does a good job of discussing their unified Tessent Connect DFT environment for managing the entire DFT process. One of the innovations here is how it helps move parts of the DFT process into the RTL stage. They also touch on how they have helped their customers meet functional safety requirements, such as ISO 26262 for the automotive market. Built-in self-test (BIST) required new features to operate in these systems. Mentor worked with ARM to put together a safety ecosystem that works for these applications.

The Mentor paper includes references to many of the partnerships that have driven and proven their DFT offerings. It also makes clear that without this level of cooperation and collaboration it would not be possible to develop such a rich and full featured solution for DFT. The full paper and its citations make interesting reading for those looking for a deep dive into their state of the art test solutions.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.