Typically, there is an existential rift between the on-chip access requirements for test and the need for security in SoCs. Using traditional deterministic scan techniques has meant opening up full read and write access to the flops in a design through the scan chains. Having this kind of access easily defeats the best designed… Read More

Tag: scan

Use Existing High Speed Interfaces for Silicon Test

The growth of complexity for silicon test as it relates to test data volume and test times is driven by multiple concurrent factors. One dimension is simply the increase in silicon complexity. However, other factors are playing a role as well. These include higher reliability requirements for new applications such as automotive,… Read More

Tessent Streaming Scan Network Brings Hierarchical Scan Test into the Modern Age

Remember when you had to use dial up internet or parallel printer cables connected directly to the printer to print something? Well even if you don’t remember these things, you know that now there is a better way. Regrettably, the prevalent methods used for hierarchical Design for Test (DFT) still look at lot like this – SoC level … Read More

Mentor Offers Next Generation DFT with Streaming Scan Network

Design for test (DFT) requires a lot of up-front planning that can be difficult to alter if testing needs or performance differ from initial expectations. Hierarchical methodologies help in many ways including making it easier to reduce on chip resources such as the number of test signals. Also, hierarchical test allows for speed-ups… Read More

DFT Innovations Come from Customer Partnerships

There is an adage that says that quality is not something that can be slapped on at the end of the design or manufacturing process. Ensuring quality requires careful thought throughout development and production. Arguably this adage is more applicable to the topic of Design for Test (DFT) than almost any other area of IC development… Read More

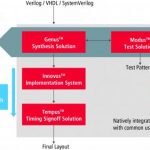

Cadence Adds New Dimension to SoC Test Solution

It requires lateral thinking in bringing new innovation into conventional solutions to age-old hard problems. While the core logic design has evolved adding multiple functionalities onto a chip, now called SoC, the structural composition of DFT (Design for Testability) has remained more or less same based on XOR-based compression… Read More

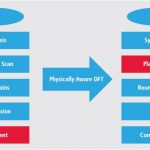

Physically Aware DFT Improves PPA

Introducing on-chip test circuitry has become a necessary criteria for an ASIC’s post manufacture testability. The test circuitry is usually referred as DFT (Design-for-Test) circuit. A typical methodology for introducing DFT circuit in a design is to replace usual flip-flops with special types of flip-flops called ‘scan… Read More

New Frontiers in Scan Diagnosis

As we move down into more and more advanced process nodes, the rules of how we test designs are having to change. One big challenge is the requirement to zoom in and fix problems by doing root cause analysis on test data alone, along with the rest of the design data such as detailed layout, optical proximity correction and so on. But without… Read More

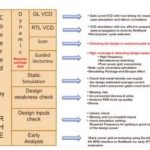

How to Assure Quality of Power and SI Verification?

As power has become one of the most important criteria in semiconductor design today, I was wondering whether there is a standard set for the power verification for an overall chip. We do have formats evolved like CPF and UPF and there are tools available to check power and signal integrity (SI), however I don’t see a standard objective… Read More

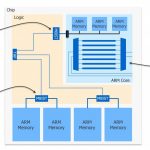

It Takes a Village: Mentor and ARM Team Up on Test

Benjamin Franklin, “I didn’t fail the test, I just found 100 ways to do it wrong.” I was reminded of this line during a joint Mentor-ARM seminar yesterday about testing ARM cores and memories. The complexity of testing modern SoC designs at advanced nodes, with multiple integrated ARM cores and other IP, opens up plenty of room for… Read More