Chiplets continue to be a hot topic on SemiWiki, conferences, white papers, webinars and one of the most active chiplet enabling vendors we work with is Synopsys. Synopsys is the #1 EDA and #1 IP company so that makes complete sense.

As you may have read, I moderated a panel on Chiplets at the last SNUG which we continue to write about. Hundreds of thousands of people around the world have read our chiplet coverage making it the #1 trending topic on SemiWiki for 2023 and I expect this to continue into 2024, absolutely.

In fact, Synopsys just released an industry insight report titled “How Quickly Will Multi-Die Systems Change Semiconductor Design?” that is well worth the read. The report also includes insights on multi-die systems from Ansys, Arm, Bosch, Google, Intel, and Samsung. Additionally, Synopsys CEO Aart de Geus wrote the opening chapter:

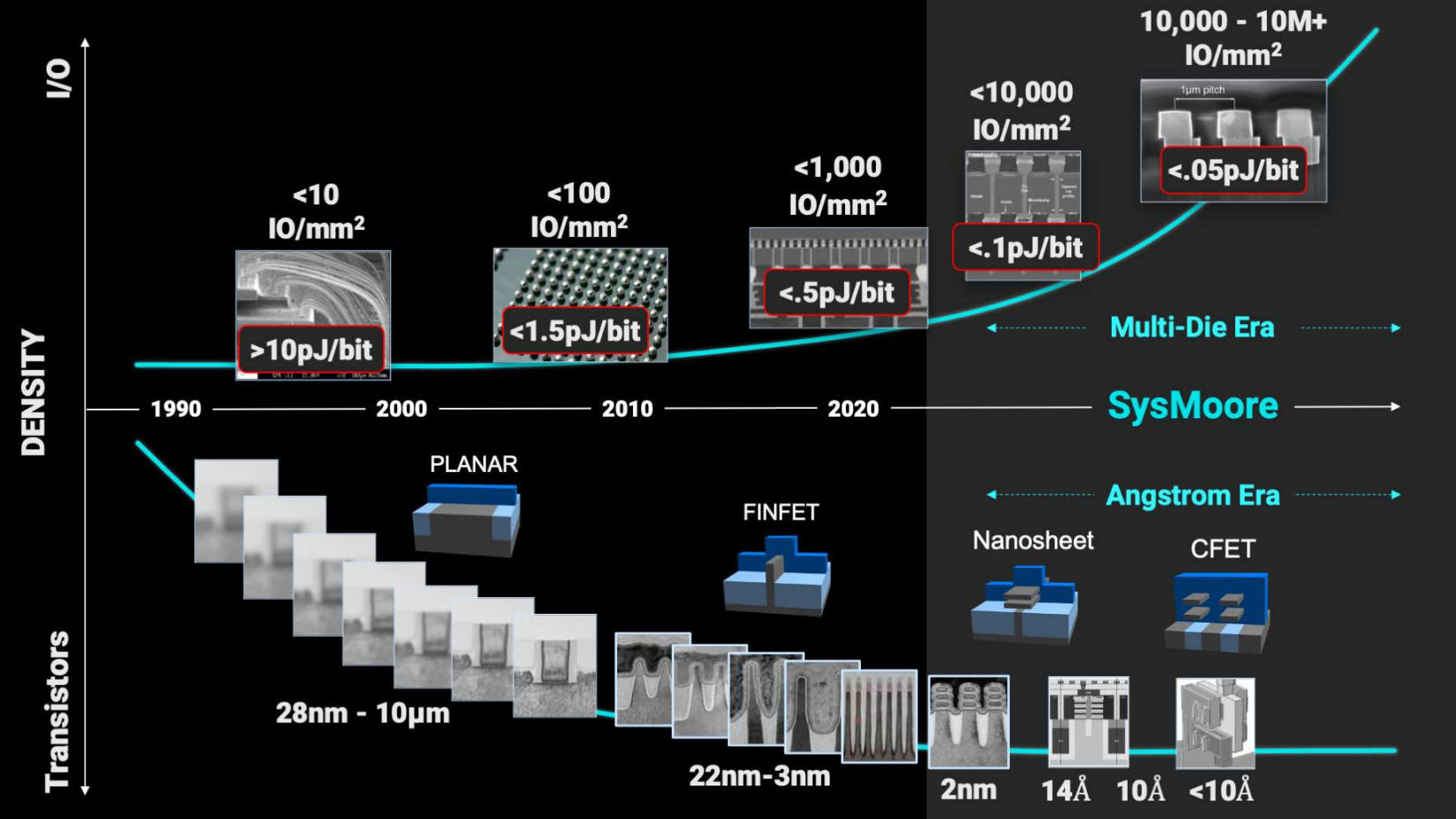

“As angstrom-sized transistors intersect with multi-die Si-substrates, we see classic Moore pass the baton to SysMoore,” writes de Geus. “Today, Synopsys tracks more than 100 multi-die system designs. Be it through hardware / software digital twins, multi-die connectivity IP, or AI-driven chip design, we collaborate closely with the leading SysMoore companies of tomorrow.”

Here is the report introduction:

For many decades, semiconductor design and implementation has been focused on monolithic, ever-larger and more complex single-chip implementation. This system-on-chip approach is now changing for a variety of reasons. The new frontier utilizes many chips assembled in new ways to deliver the required form-factor and performance.

Multi-die systems are paving the way for new types of semiconductor devices that fuel new products and new user experiences.

This Synopsys Industry Insight brings together a select group of keystone companies who are advancing multi-die systems. You’ll read the thoughts of senior executives from various levels of the technology stack. You’ll also hear from Synopsys’ CEO, its president and a panel of Synopsys technology experts. We’ll discuss our achievements, what lies ahead and how we are partnering with the industry to drive change.

Synopsys also recently completed an excellent webinar series on the topic which is well worth your time. You can watch this On-Demand HERE.

Synopsys Chiplet Webinar Series abstract:

The industry is moving to multi-die systems to benefit from the greater compute performance, increased functionality, and new levels of flexibility. Challenges for multi-die systems are exacerbated and require greater focus on a number of requirements such as early partitioning and thermal planning, die/package co-design, secure and robust die-to-die connectivity, reliability and health, as well as verification and system validation. Attend this webinar series to find out about some of the essential requirements that can help you overcome multi-die system challenges and make your move to multi-die systems successful.

Topics include:

- Multi-Die System Trends, Challenges and Requirements

- Benefits of Early Architecture Design for Multi-Die Systems

- Innovations in Multi-Die System Co-Design and System Analysis

- Successful Connectivity of Heterogeneous Dies with UCIe IP

- Identifying and Overcoming Multi-Die System Verification Challenges

- Optimizing Multi-Die System Health from Die to Package to In-Field

Bottom line: Chiplets are a disruptive technology driving the semiconductor design ecosystem without a doubt. If you want to explore chiplets in greater detail Synopsys would be a great start.

Also read:

Chiplet Interconnect Challenges and Standards

Chiplet Q&A with Henry Sheng of Synopsys

Chiplet Q&A with John Lee of Ansys

Multi-Die Systems: The Biggest Disruption in Computing for Years

Comments

There are no comments yet.

You must register or log in to view/post comments.