We all know (I hope) that security is important so we’re willing to invest time and money in this area but there are a couple of problems. First there’s no point in making your design secure if it’s not competitive and making it competitive is hard enough, so the great majority of resource and investment is going to go into that objective.… Read More

FPGA Landscape Update 2019

In 2015 Intel acquired Altera for $16.7B changing one of the most heated rivalries (Xilinx vs Altera) the fabless semiconductor ecosystem has ever seen. Prior to the acquisition the FPGA market was fairly evenly split between Xilinx and Altera with Lattice and Actel playing to market niches in the shadows. There were also two FPGA… Read More

Webinar: ASIC and FPGA Functional Verification Study

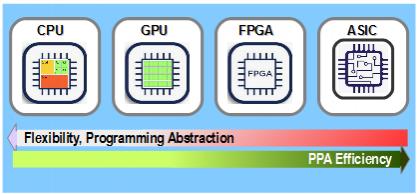

ASIC or FPGA? Each design style has earned designers’ votes depending on the level of urgency, application complexity and funding of their assigned projects. While it is feasible to transition from ASIC to FPGA design or vice versa, such a move is usually done across project refresh instead of midcourse.

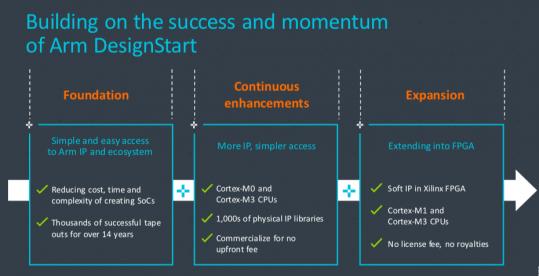

One Less Reason to Delay that Venture

Many of us dream about the wonderful widget we could build that would revolutionize our homes, parking, health, gaming, factories or whatever domain gets our creative juices surging, but how many of us take it the next step? Even when you’re ready to live on your savings, prototypes can be expensive and royalties add to the pain. … Read More

FPGA, Data and CASPA: Spring into AI (2 of 2)

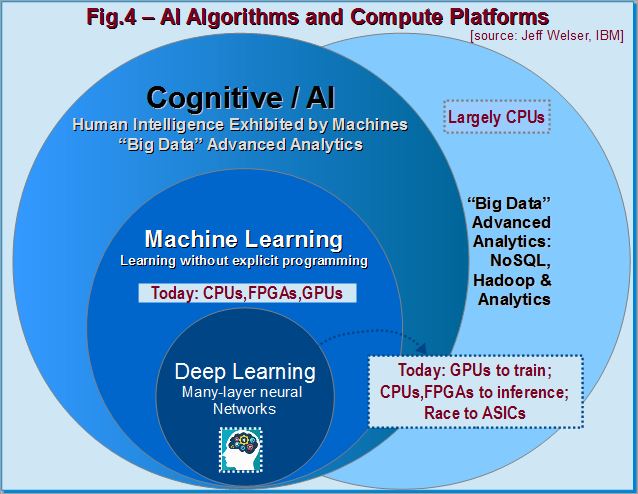

Adding color to the talks, Dr. Jeff Welser, VP and IBM Almaden Research Lab Director showed how AI and recent computing resources could be harnessed to contain data explosion. Unstructured data growth by 2020 would be in the order of 50 Zetta-bytes (with 21 zeros). One example, the Summit supercomputer developed by IBM for use at… Read More

FPGA, Data and CASPA: Spring into AI

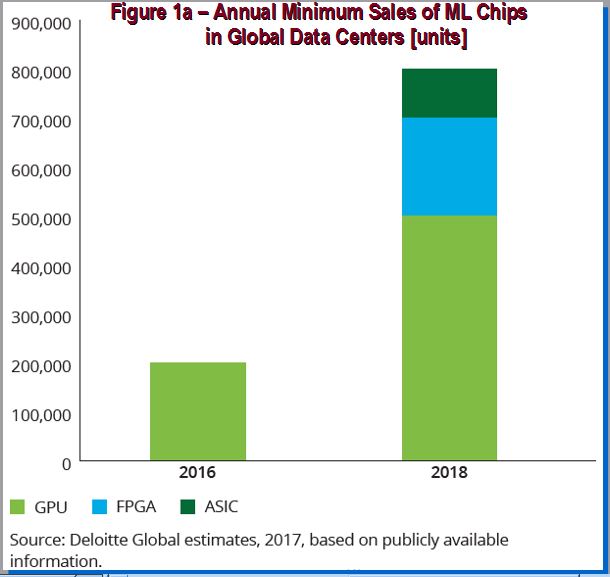

Just like good ideas percolate longer, we have seen AI adoption pace picking-up speed, propelled by faster GPUs. Some recent data points provide good indication that FPGA making a comeback to bridge chip-design needs to keep-up with AI’s ML applications.

According to the Deloitte research firm there is a projected increase of… Read More

A Self-Contained Software-Driven Prototype

You’re building an IP, subsystem or SoC and you want to use a prototype together with a software testbench to drive extensive validation testing. I’m not talking here about the software running on the IP/SoC processor(s); the testbench should wrap around the whole DUT. This is a very common requirement. The standard approach to… Read More

Xilinx vs Altera Update 2017

I truly miss the Xilinx versus Altera war of words (competition at its finest) and competition is what makes the fabless semiconductor ecosystem truly great, absolutely. So with great disappointment I read the Intel Analyst Day transcript published by Bloomberg last week. It is attached at the bottom in case you are interested… Read More

3 in 1 Hardware Verification

Aldec has offered front-end EDA tools for over 30 years but may not be a familiar name to mainstream IC design engineers. That’s probably because for most that period they haven’t really targeted IC design. They have been much more focused on PC-based design for FPGAs particularly where requirements traceability has been important,… Read More

FPGAs for a few thousand devices more

An incredibly pervasive trend at last year’s ARM TechCon was the IoT, and I expect this year to bring even more of the same, but with a twist. Where last year was mostly focused on ultra-low power edge devices and the mbed ecosystem, this year is likely to show a better balance of ideas across all three IoT tiers. I also expect a slew of … Read More

Solving the EDA tool fragmentation crisis