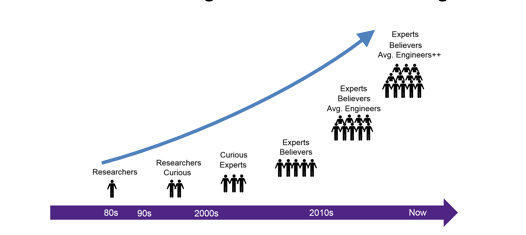

I assume you know the Geoffrey Moore “crossing the chasm” concept, jumping from early stage enthusiasts trying your product because they’ll try anything new, to expanding to a mainstream and intrinsically more critical audience – a much tougher proposition. I’d argue there may be more than one of these transitions in the… Read More

Automotive Design and Virtual Prototyping

The entire history of EDA software tools has enabled engineers to design ICs and SoCs using virtual prototyping, so most of us in the industry are familiar with the idea of modeling and simulating something as complex as an IC before actually starting the manufacturing process. In a complex system like an automobile there are a lot… Read More

Learning on the Edge Investment Thesis

It is said that it will cost as much as $600M to develop a 5nm chip. At that price, only a few companies can afford to play, and with that amount of cash in, innovation is severely limited.

At the same time, there is a stampede in the artificial intelligence (AI) market where around 60 startups have appeared, many of which have already … Read More

The IoT will meet 5G soon, but not with the old SIM cards

By now you have probably realized that 5G is a lot more than an incremental change from previous 3G and 4G cellular technology. For instance, 5G will be used to connect our phones in completely new ways, such as with microcells in urban areas using mm-wavelength signals. 5G will also include two low power protocols that are intended… Read More

Re Energizing Silicon Innovation

Hardware is roaring back into prominence in technology innovation, from advanced cars to robots, smart homes and smart cities, 5G communication and the burgeoning electronification of industry, medicine and utilities. While software continues to play a role, all of these capabilities depend fundamentally on advances in … Read More

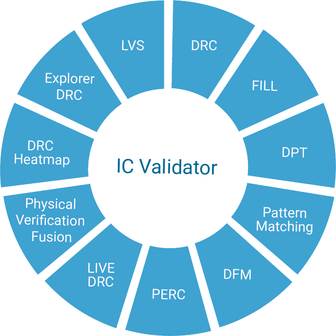

Complex Validation Requires Scalable Measures

The famous Olympic motto Citius, Altius, Fortius, which is the Latin words for “Faster, Higher, Stronger” to a considerable degree can be adapted to our electronics industry. Traditionally the fundamental metrics we used for measuring the quality of results (QoRs) are performance, power, and area (PPA). Amidst… Read More

EDA Update 2019

Over the last six years EDA has experienced yet another disruption not unlike the Synopsys acquisition of Avant! in 2001 which positioned Synopsys for the EDA lead they still enjoy today. Or the hiring of famed venture capitalist Lip-Bu Tan in 2009 to be the CEO of struggling EDA pioneer Cadence Design Systems. Under Lip-Bu’s… Read More

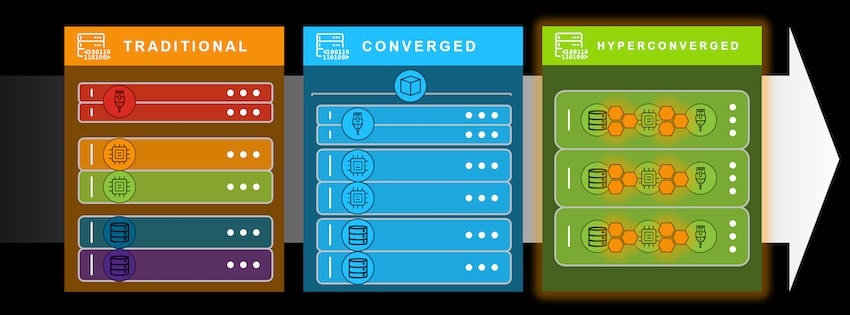

IC Implementation Improved by Hyperconvergence of Tools

Physical IC design is a time consuming and error prone process that begs for automation in the form of clever EDA tools that understand the inter-relationships between logic synthesis, IC layout, test and sign-off analysis. There’s even an annual conference called ISPD – International Symposium on Physical Design… Read More

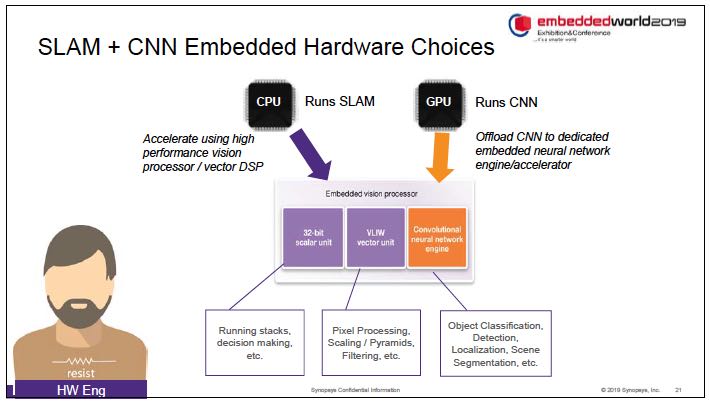

Using ML to Build Efficient Low Power Platforms for Augmented Vision

We are all pretty familiar with augmented reality, where real world images are overlaid with computer generated images, graphics and even audio. Of course, our first exposure to augmented reality might have been images of heads up displays in fighter jets or perhaps in the movie The Terminator. Augmented reality is moving rapidly… Read More

Managing Formal Complexity Even into AI

The Synopsys Formal group have a reputation for putting on comprehensive tutorials/workshops at DVCon and this year again they did not disappoint. The theme for the Thursday workshop was tackling complexity in control and datapath designs using formal. Ravindra Aneja, who I know from Atrenta days, kicked off the session with… Read More