How could we differentiate between deep learning and machine learning as there are many ways of describing them? A simple definition of these software terms can be found here. Let’s look into Artificial Intelligence (AI), which was coined back in 1956. The term AI can be defined as human intelligence exhibited by machines.… Read More

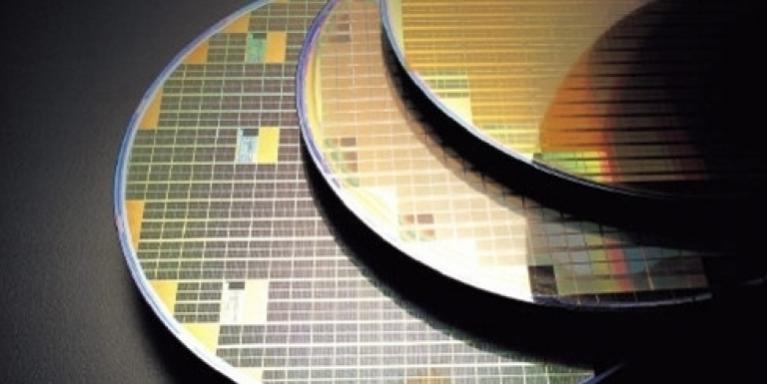

TSMC 5nm and EUV Update 2018

The TSMC Q4 2017 earnings call transcript is up and I found it to be quite interesting for several reasons. First and foremost, this is the last call Chairman Dr. Morris Chang will participate in which signifies the end of a world changing era for me and the fabless semiconductor ecosystem, absolutely. TSMC announced his retirement… Read More

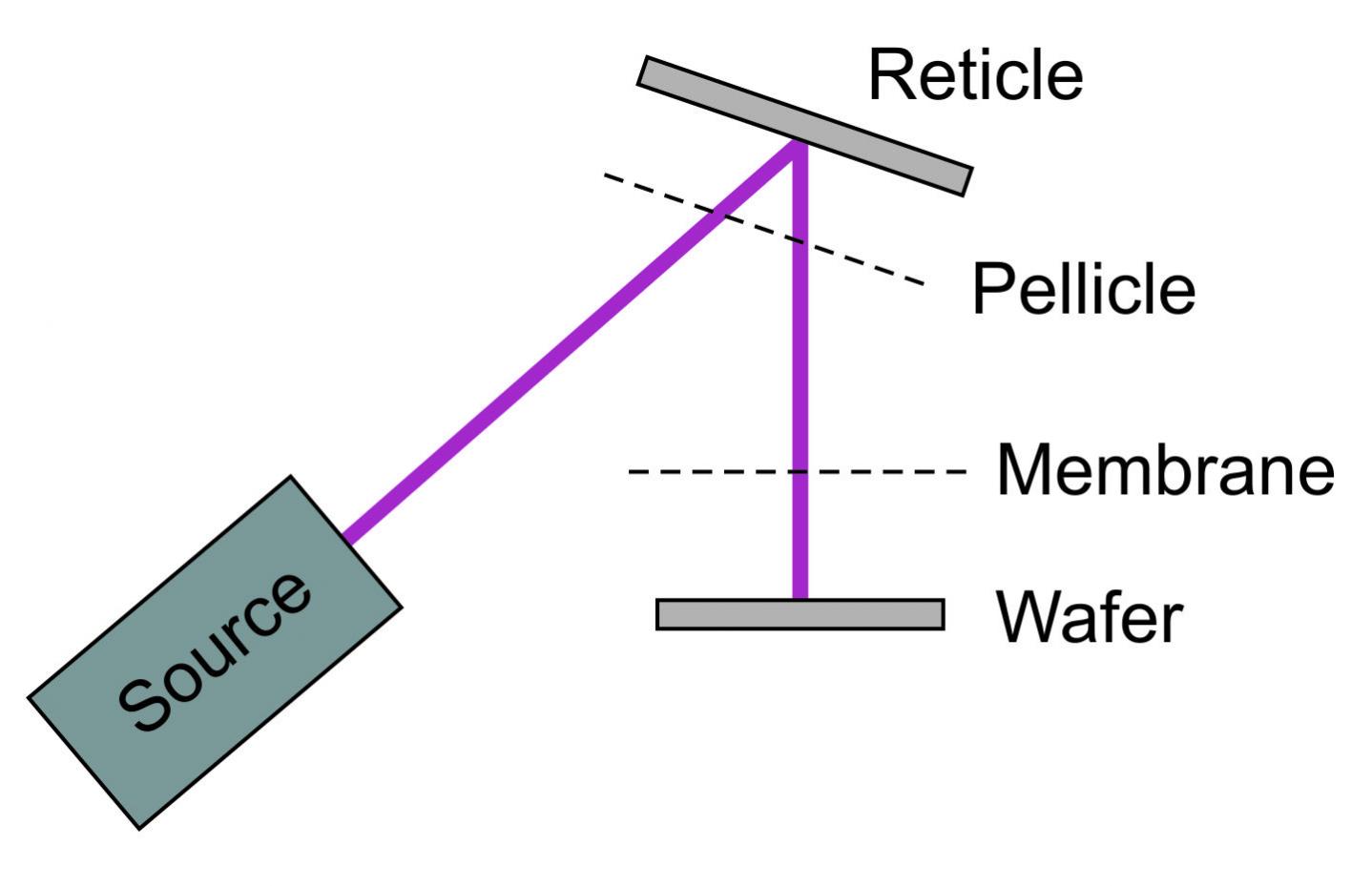

ISS 2018 – The Impact of EUV on the Semiconductor Supply Chain

I was invited to give a talk at the ISS conference on the Impact of EUV on the Semiconductor Supply Chain. The ISS conference is an annual gathering of semiconductor executives to review technology and global trends. In this article I will walk through my presentation and conclusions.… Read More

ASIC and TSMC are the AI Chip Unsung Heroes

One of the more exciting design start market segments that we track is Artificial Intelligence related ASICs. With NVIDIA making billions upon billions of dollars repurposing GPUs as AI engines in the cloud, the Application Specific Integrated Circuit business was sure to follow. Google now has its Tensor Processing Unit, Intel… Read More

Choosing the lesser of 2 evils EUV vs Multi Patterning!

For Halloween this week we thought it would be appropriate to talk about things that strike fear into the hearts of semiconductor makers and process engineers toiling away in fabs. Do I want to do multi-patterning with the huge increase in complexity, number of steps, masks and tools or do I want to do EUV with unproven tools, unproven… Read More

Arm TechCon Preview with the Foundries!

This week Dr. Eric Esteve, Dr. Bernard Murphy, and I will be blogging live from Arm TechCon. It really looks like it will be a great conference so you should see some interesting blogs in the coming days. One of the topics I am interested in this year is foundation IP and I will tell you why.

During the fabless transformation of the semiconductor… Read More

TSMC: Semiconductors in the next ten years!

The TSMC 30th Anniversary Forum just ended so I will share a few notes before the rest of the media chimes in. The forum was live streamed on tsmc.com, hopefully it will be available for replay. The ballroom at the Grand Hyatt in Taipei was filled with cameras, semiconductor executives, and security personnel.

The… Read More

TSMC Teamwork Translates to Technical Triumph

Most people think that designing successful high speed analog circuits requires a mixture of magic, skill and lots of hard work. While this might be true, in reality it also requires a large dose of collaboration among each of the members of the design, tool and fabrication panoply. This point was recently made abundantly clear … Read More

TSMC OIP and the Insatiable Computing Trend!

This year’s OIP was much more lighthearted than I remember which is understandable. TSMC is executing flawlessly, delivering new process technology every year. Last year’s opening speaker, David Keller, used the phrase “Celebrate the way we collaborate” which served as the theme for the conference. This year David’s… Read More

Breakfast with Aart de Geus and the Foundries!

Being the number one EDA and the number one IP company does have its advantages and the resulting foundry relationships are a clear example. One of the DAC traditions that I truly enjoy is the Synopsys foundry breakfasts. Not only does Synopsys welcome scribes, they reserve a table up front for us and Synopsys CEO Aart de Geus has been… Read More