You’re building an IP, subsystem or SoC and you want to use a prototype together with a software testbench to drive extensive validation testing. I’m not talking here about the software running on the IP/SoC processor(s); the testbench should wrap around the whole DUT. This is a very common requirement. The standard approach to… Read More

FPGA based Prototyping

Prototype-Based Debug for Cloud Design

Unless you’ve been in hibernation for a while, you probably know that a lot more chip design is happening in system companies these days. This isn’t just for science experiments; many of these designs are already being used in high-value applications. This development is captive – systems companies generally don’t want… Read More

Anirudh on Verification

I was fortunate to have a 1-on-1 with Anirudh before he delivered the keynote at DVCon. In case you don’t know the name, Dr. Anirudh Devgan is Executive VP and GM of the Digital & Signoff Group and the System & Verification Group at Cadence. He’s on a meteoric rise in the company, not least for what he has done for Cadence’s position… Read More

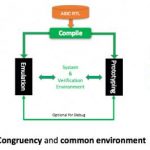

Prototyping: Sooner, Easier, Congruent

DVCon 2017 is a big week for Cadence verification announcements. They just released their Xcelium simulation acceleration product (on which I have another blog) and they have also released their latest and greatest prototyping solution in the Protium S1. This is new hardware based on Virtex UltraScale FPGAs on Cadence-designed… Read More

Aspirational Congruence

When talking to suppliers about their products, conversation tends to focus heavily on what they already have and why it is the answer to every imaginable need in their space. So it’s refreshing when a vendor wants to talk about where customers want to go without claiming they already have the answer wrapped up in a bow. I recently … Read More

CEO Interview: Toshio Nakama of S2C

I haven’t sat down to speak with S2C since we collaborated on the book, PROTOTYPICAL, published just before DAC 2016 and even then, I hadn’t spoken to Toshio Nakama, their CEO. Toshio splits his time between the San Jose headquarters and the Shanghai headquarters so getting time to meet face-to-face has been challenging. I was finally… Read More

The Future of FPGA Prototyping!

This interview originally appeared as the foreword to our book “Prototypical: The Emergence of FPGA-based Prototyping for SoC Design” but I thought it would be worth publishing for those of you who have not downloaded it yet. I also wanted to mention that our friends at S2C are currently offering a 50% discount on the… Read More

OpenCL hits FPGA-based prototyping modules

OpenCL brings algorithm development into a unified programming model regardless of the core, working across CPUs, GPUs, DSPs, and even FPGAs. Intel has been pushing OpenCL programming for some time, particularly at the high end with “Knights Landing” processors. Where other vendors are focused on straight-up C high-level … Read More

3 in 1 Hardware Verification

Aldec has offered front-end EDA tools for over 30 years but may not be a familiar name to mainstream IC design engineers. That’s probably because for most that period they haven’t really targeted IC design. They have been much more focused on PC-based design for FPGAs particularly where requirements traceability has been important,… Read More

Protium for the win in software development

Cadence Design Systems is a long-standing provider in hardware emulation, but a relative newcomer to FPGA-based prototyping. In an upcoming lunch and learn session on November 11 in San Jose, Cadence teams will be outlining their productivity strategy. What’s different with their approach and why is this worth a lunch?… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?