You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 16126

[name] => Lithography

[slug] => lithography

[term_group] => 0

[term_taxonomy_id] => 16126

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 187

[filter] => raw

[cat_ID] => 16126

[category_count] => 187

[category_description] =>

[cat_name] => Lithography

[category_nicename] => lithography

[category_parent] => 0

[is_post] =>

)

-If you can’t beat them, embargo them

-It has been reported US wants ASML to halt China DUV tools

-US obviously wants to kill, not just wound China chip biz

-Is this embargo the alternative to failed CHIPS act?

-Hard to say “do as I say, not as I do”- but US does anyway

First EUV ban now DUV ban? Are process & yield… Read More

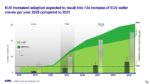

At the 2022 SPIE Advanced Lithography Conference, ASML presented an update on EUV. I recently had a chance to go over the presentations with Mike Lercel of ASML. The following is a summary of our discussions.

0.33 NA

The 0.33 NA EUV systems are the production workhorse systems for leading edge lithography today. 0.33 NA systems are… Read More

The next generation of EUV lithography systems are based on a numerical aperture (NA) of 0.55, a 67% increase from the current value of 0.33. It targets being able to print 16 nm pitch [1]. The High-NA systems are already expected to face complications from four issues: (1) reduced depth-of-focus requires thinner resists, which… Read More

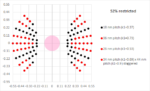

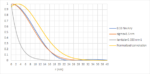

To the general public, EUV lithography’s resolution can be traced back to its short wavelengths (13.2-13.8 nm), but the true printed resolution has always been affected by the stochastic behavior of the electrons released by EUV absorption [1-5].

A 0.33 NA EUV system is expected to have a diffraction-limited point spread… Read More

At this year’s SPIE Advanced Lithography conference, changes to EUV masks were particularly highlighted, as a better understanding of their behavior is becoming clear. It’s now confirmed that a seemingly symmetric EUV mask absorber pattern does not produce a symmetric image at the wafer, as a conventional DUV … Read More

As a consequence of having a ~13.5 nm wavelength, EUV photons transfer ~90% of their energy to ionized photoelectrons. Thus, EUV lithography is fundamentally mostly EUV photoelectron lithography. The actual resolution becomes dependent on photoelectron trajectories.

Photoelectron trajectories in EUV lithography were… Read More

The list of possible stochastic patterning issues for EUV lithography keeps growing longer: CD variation, edge roughness, placement error, defects [1]. The origins of stochastic behavior are now well-known. For a given EUV photon flux into the resist, a limited fraction are absorbed. Since the absorption is less than 5% affected… Read More

In my “The EUV Divide and Intel Foundry Services” article available here, I discussed the looming EUV shortage. Two days ago, Intel announced their first EUV tool installed at their new Fab 34 in Ireland is a tool they moved from Oregon. This is another indication of the scarcity of EUV tools.

I have been tracking EUV system production… Read More

At the ISS conference held from April 4th through 6th I presented on who I thought would have the leading logic technology in 2025. The following is a write up of that presentation.

ISS was a virtual conference in 2021 and I presented on who currently had logic leadership and declared TSMC the clear leader. Following that conference,… Read More

Stochastic defects continue to draw attention in the area of EUV lithography. It is now widely recognized that stochastic issues not only come from photon shot noise due to low (absorbed) EUV photon density, but also the resist material and process factors [1-4].

It stands to reason that resist absorption of EUV light, which is … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era