You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 725

[filter] => raw

[cat_ID] => 14

[category_count] => 725

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 725

[filter] => raw

[cat_ID] => 14

[category_count] => 725

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

On Monday Synopsys announced that it was acquiring Elliptic Technologies. They have one of the largest portfolios of security IP consisting of both semiconductor IP blocks and software. Increasingly, security requires a multi-layer approach involving both secure blocks on the chip and a software stack on top of that.

Elliptic’s… Read More

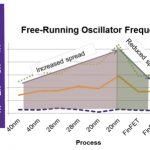

One of the most interesting presentations that I went to was the last presentation at the Synopsys Custom Lunch (no, the lunch wasn’t custom, we all got the same, but the presentations were about custom design). Since the last presentation was by Synopsys themselves and not by a customer, it wouldn’t seem promising that it could … Read More

The Design Automation Conference is the largest and most diverse event in the fabless semiconductor ecosystem. Next week in San Francisco you will see technology and people you have never seen before. You will benefit from the efforts of hundreds of thousands of semiconductor professionals like myself who have dedicated their… Read More

By offering low-power PCI Express PHY solution for mobile application! To make it clear, we are not talking about Mobile Express (M-PCIe), but clearly about PCI Express protocol, including a PCIe Controller and a PCIe PHY. Initially developed to support internal connection between the CPU and the GPU in a PC, the technology has… Read More

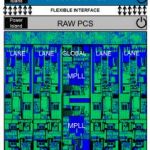

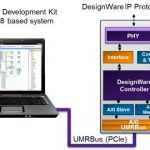

Hybrid IP Prototyping Kit from Synopsys!

Synopsys has launched IP Accelerated initiative last year. The goal was clearly to accelerate Time-To-Market by providing a complete set of “tools” to augment design productivity:

- IP Prototyping Kit with reference designs work out-of-the-box

- IP software development kits enable early

…

Read More

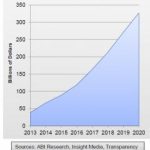

Before answering the question we should try to define what is behind “Vision”, which type of applications and evaluate this heterogeneous market weight. Embedded Vision (EV) is the use of computer vision in embedded systems to interpret meaning from image or video. In fact vision processing requires a lot of maths functions that… Read More

Earlier this week it was the Synopsys user group meeting SNUG. Not just any old SNUG but the 25th Annual SNUG. The first one was 15th March 1991 and was attended by 100 people. At the time, Synopsys had annual revenues of $22M. This year, the various SNUGs around the world will have a total attendance of 10,000 people and Synopsys revenue… Read More

Today an SoC cannot be without multiple IP blocks integrated together in the most optimal manner. In such an environment, it’s natural that interoperability and configurability of an IP get prime considerations to achieve the best PPA (Power, Performance and Area) for the SoC containing that IP. While PPA is a basic criterion … Read More

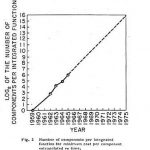

Lately there has been significant concern over the rising costs of designing in silicon and the troubling decline in venture investments in semiconductors. These alarming trends include fewer IPOs, a falloff in the amount and frequency of early stage seed investments, and comparatively low industry organic growth rates. A … Read More

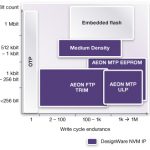

As of today NVM IP has been mostly used in SoC or IC to support very specific needs like analog trimming and calibration or encryption key integration for Digital Right Management (DRM) purpose. In other words small size (less than 1K-bit) few times programmable (FTP) NVM IP was enough to support these needs, thus most of the NVM IP… Read More