The trend of AI augmentation into many facets of silicon based hardware applications is on the rise. During the CASPA press conference in Santa Clara last week, Silvaco CEO David Dutton and SiFive VP, GM Christopher Moezzi were present to share their insights.

Silvaco CEO David Dutton mentioned that we are in new era in which many… Read More

Semiconductor Intellectual Property

Radar is Cheaper but Autonomous Car Needs Lidar!

To replace a human driver, autonomous car will have to “see” and do it in a better way than human being. The available solution, based on camera, radar, lidar, is not perfect and need to be improved. Radar is great for “seeing” in bad weather but has insufficient resolution to distinguish distant objects. Lidar produces high-resolution… Read More

Synopsys GLOBALFOUNDRIES and Automotive IP

IP vendors have always had the inside track on the status of new process nodes and what customers are planning for their next designs. This is even more apparent now that systems companies are successfully doing their own chips by leveraging the massive amounts of commercial IP available today. Proving once again that IP really … Read More

Can I Trust my Hardware Root of Trust?

Hardware Roots of Trust (HRoTs) have become a popular mechanism to provide a foundational level of security in a cell-phone or IoT device or indeed any device that might appear to a hacker to be a juicy target. The concept is simple. In order to offer credible levels of security, any level in the stack has to be able to trust that levels… Read More

Safety: Big Opportunity, A Long and Hard Road

Safety, especially in road vehicles (cars, trucks, motorcycles, etc.), gets a lot of press these days. From the point of view of vendors near the bottom of the value chain it can seem that this just adds another item to the list of product requirements; as long as you have that covered, everything else remains pretty much the same in… Read More

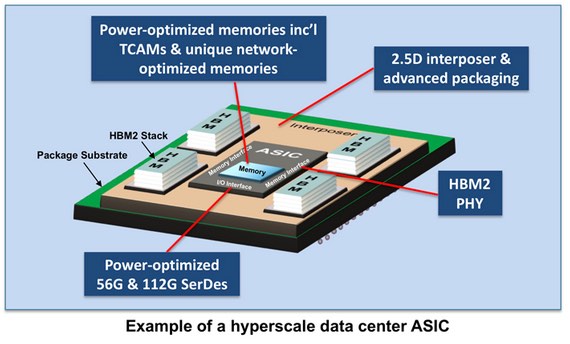

eSilicon Expands Expertise in 7nm

At SemiWiki we usually don’t write about the press releases we are sent. However, a recent press release by eSilicon caught my eye and prompted me to call Mike Gianfagna, eSilicon Vice President of Marketing. The press release is not just about one thing, rather it focuses on a number of interesting things that together show their… Read More

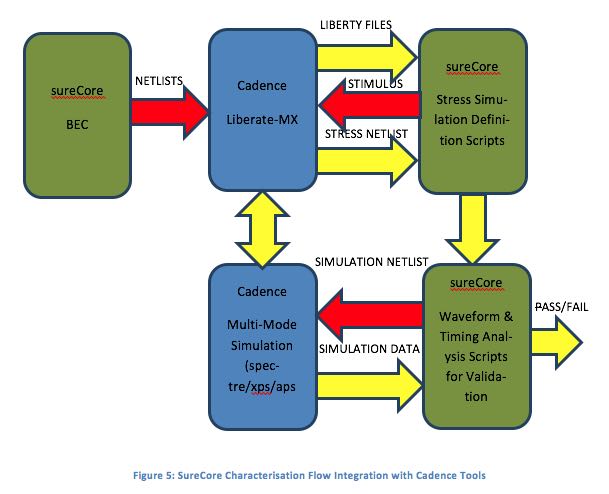

Low Power SRAM Complier and Characterization Enable IoT Applications

If you are designing an SOC for an IoT application and looking to minimize power consumption, there are a lot of choices. However, more often than not, looking at reducing SRAM power is a good place to start. SRAMs can consume up to 70% of an IC’s power. SureCore, a leading memory IP supplier, offers highly optimized SRAM instances … Read More

The RISC-V Revolution is Going Global!

This Month, you can Join us in Austin, Mountain View or Boston

In 2018, we hosted several RISC-V technology symposia in India, China and Israel. These events were very successful in fueling the growing momentum surrounding the RISC-V ISA in these countries. It turns out that these events were just the tip of the iceberg. In 2019, … Read More

The Best Way to Keep a Secret

Anyone knows that the best way to keep a secret is never to share it with anyone. Which works fine for your own most personal secrets, but it’s not very useful when you have to share with at least one other, such as in cyber-security. One such need, of enormous importance in the IoT, is authentication; are you who you claim to be? Seas of… Read More

Top 3 Reasons Why Design IP Is Business Friendly

The Design IP market is doing well, growing at higher CAGR that the semiconductor market it is serving, in fact 10% higher for 2007-2017! You may wonder why this IP market is so business friendly? I will try to answer and propose the top 3 reasons explaining this behavior. To name it: IP business is recurrent, external IP sourcing is… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era