You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 178

[name] => IP

[slug] => ip

[term_group] => 0

[term_taxonomy_id] => 178

[taxonomy] => category

[description] => Semiconductor Intellectual Property

[parent] => 0

[count] => 2023

[filter] => raw

[cat_ID] => 178

[category_count] => 2023

[category_description] => Semiconductor Intellectual Property

[cat_name] => IP

[category_nicename] => ip

[category_parent] => 0

[is_post] =>

)

ARM SoC Hardeningby Daniel Payne on 05-30-2013 at 3:11 pmCategories: Arm, IP

Last year at DACI discovered a physical IP company called DXCorrthat competed against giant ARM. This year the company has selected a different direction, so I got caught up with Nirmalya Ghosh, the CEO to hear about the changes.

Nirmalya Ghosh, DXCorr

… Read More

In 2002 few people outside of Steve Jobs, could have predicted the iPhone. But a forward-looking technology CEO could expect Moore’s Law to extend into portable devices as it did with PCs. While 2G and 2.5G cellular phones were shipping in the hundreds of millions, the features were rather primitive. 3G, 4G, WiFi, Bluetooth,… Read More

I have mentioned NoC adoption explosion during the last two years, illustrated by the huge revenue growth of Arteris. This trend is now confirmed in the fastest moving segments, the Application Processors (AP) and LTE Modem for mobile applications. In fact, Arteris FlexNoC has been integrated in the majority of AP and LTE Modem… Read More

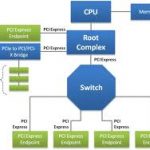

PCI Express 3.0 specification is 1000 pages long. Most of us, and most of the designers integrating PCIe gen-3 into their latest ASIC, FPGA or system will probably never read it completely, or even open it. In fact, they don’t need to read it completely, but they should care about one point, whether they buy an ASSP or a PCIe design IP:… Read More

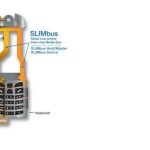

As we know mobile industry is one of the fastest growing in the electronics arena, and it has led to the emergence of several standards of interfaces between processors, devices, storage, camera, keyboard and so on. The interfaces can involve hardware as well as software and can be complex. The standards are still evolving, often… Read More

Carbon Design drives a lot of traffic to SemiWiki. Actually, it’s ARM driving traffic to the Carbon landing page since Carbon and ARM work closely together. When we blog about designing with ARM IP droves of people click over. Seriously, DROVES of people. Rick Lucier has deep EDA experience and has led Carbon as CEO for the … Read More

Recently, Sonics and ARM entered into an agreement whereby ARM licensed a significant portion of Sonics’ patent portfolio. Sonics, Inc. is one of the leading providers of connectivity IP often referred to as network-on-chip, or NoC. ARM is the leading provider of processor intellectual property (IP). The potential scope… Read More

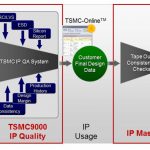

Talking about Design IP (I mean successful Design IP) lead you to quickly pronounce the two magic key words: Quality and Ecosystem. Those who remember the IP emergence in the mid 90’s know very well why Quality has to be a prerequisite when dealing with Design IP, as they probably have paid the price of mediocre IP quality at that time.… Read More

It was definitely a good idea to go to Munich to listen to the keynote talk from Lip-Bu Tan. Did I learned in direct live the name of the next acquisition from Cadence in 2013, after Tensilica and Cosmic Circuits? Yes and the winner is… Evatronix! And cadence as well as Evatronix is enjoying more than 600 customers worldwide, thanks … Read More

Storage interfaces for mobile are evolving rapidly, in particular with the Universal Flash Storage (UFS) standard. So how do you test a design? If you want to test a design that accesses, say, an SD card then you can wander into Fry’s and buy an SD card for a few dollars. But to design an interface to UFS is a bit harder since the … Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior