There is obviously a lot going on in 3D IC these days. And I don’t mean at the micro level of FinFETs which is also a way of going vertical. I mean through-silicon-via (TSV) based approaches for either stacking die or putting them on an interposer. Increasingly the question is no longer if this technology will be viable (there… Read More

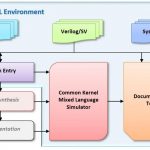

An FPGA Design Flow with Aldec Tools

I’ve used FPGA vendor-supplied tools from both Xilinxand Lattice Semibefore, so I wanted to see what EDA tools Aldec has to offer for FPGA design. I read the Aldecwhite paper, Corporate Standardization of FPGA Design Flow, and summarize what I found.… Read More

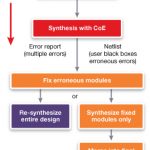

Second FPGA to the right, and straight on ‘til it works

In a fantasy world where there were no coding errors or integration issues, FPGA designs would fly straight through synthesis easily and quickly. Maybe that world does exist somewhere. For the rest of us, who have experienced the agony of running a large FPGA design – again – only to find another error and have to start over, there … Read More

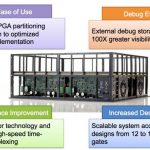

What I Learned About FPGA-based Prototyping

Today I attended an Aldec webinar about ASIC and SoC prototyping using the new HES-7 Board. This prototyping board is based on the latest Virtex-7 FPGA chips from Xilinx.

You can view the recorded webinar here, which takes about 30 minutes (should be available in a few days). I first blogged about the HES-7 two months ago, ASIC Prototyping… Read More

The logic of trusting FPGAs through DO-254

Any doubters of the importance of FPGA technology to the defense/aerospace industry should consider this: each Airbus A380 has over 1000 Microsemi FPGAs on board. That is a staggering figure, especially considering the FAA doesn’t trust FPGAs, or the code that goes into them.… Read More

Next Generation FPGA Prototyping

One technology that has quietly gone mainstream in semiconductor design is FPGA prototyping. That is, using an FPGA version of the design to run extensive verification. There are two approaches to doing this. The first way is simply to build an prototype board, buy some FPGAs from Xilinx or Altera and do everything yourself. The… Read More

Xilinx Programmable Packet Processor

At the Linley conference last week I ran into Gordon Brebner of Xilinx. He and I go a long way back. We had adjacent offices in Edinburgh University Computer Science Department back when we were doing our PhDs and conspiring to network the department’s Vax into the university network over a two-week vacation. We managed to … Read More

12m FPGA prototyping sans partitioning

FPGA-based prototyping brings SoC designers the possibility of a high-fidelity model running at near real-world speeds – at least until the RTL design gets too big, when partitioning creeps into the process and starts affecting the hoped-for results.

The average ASIC or ASSP today is on the order of 8 to 10M gates, and that includes… Read More

Altera’s Real Impact with ARM based SOC FPGAs

At the annual Linley Processor Conference this past week a number of chip vendors proposed a raft of new networking solutions directed at solving today’s bandwidth issues. Perhaps the overall highlight of the conference was the recognition by Keynote Speaker Linley Gwennap of the shift that is taking place towards ARM based solutions.… Read More

Altera’s Use of Virtual Platforms

Altera have been making use of Synopsys’s virtual platform technology to accelerate the time to volume by letting software development proceed in parallel with semiconductor development so that the software development does not need to wait until availability of hardware.

In the past, creating the virtual platform … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center