Back in the days where computing was dominated by a few big (and now mostly dearly departed) names, there was a saying: “Nobody ever got fired for buying IBM.” The relative safety of immediate brand recognition, especially among non-technical upper management, dissuaded many users from recommending or even seeking out other … Read More

Xilinx: Delivering a Generation Ahead

Last week was Xilinx’s investor day. Xilinx believe they are now a process generation ahead. They did over $100M in 28nm designs in FY2013 (Xilinx FY ended March 2013) and did over over $100M in Q4 2013 calendar year alone (and this is almost all true production volume, with only about 5% prototypes) with a plan greater than … Read More

Happy Birthday Xilinx

I have never done this before, wished a company happy birthday. So here goes, Happy Birthday Xilinx! How does it feel to be 30? Looking good eh? Signing up for AARP? My family and I just sang and had cake and ice cream. They did look at me like I was nuts when I set a place at the table for a Xilinx FPGA. In all seriousness, over the years Xilinx… Read More

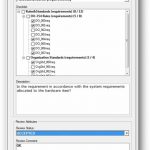

If requirements ask for it, it had better be there

Engineers are known for their attention to detail and precision in thinking, but sometimes still struggle during compliance audits. This is especially true the longer a list of requirements becomes, especially unstructured lists kept in spreadsheets and on Post-It notes.

It gets even more complicated, because in defense circles… Read More

Xilinx’s Mixed Signal FPGA

Something in all the Xilinx chatter of UltraScale 20nm, 16nm, having massive amounts of Gigabit transceivers, DSP blocks, RAM, HLS, Rapid Design Closure gets lost… and that is Xilinx’s ability for Mixed Signals. I do not mean when you are talking with the wife (Remember Listen!), but a wonderful block that lives within… Read More

Technology Challenges: Intel, IBM, Xilinx, GlobalFoundries, IMEC

I spent the day at the SEMI Industry Strategy Symposium in Half Moon Bay. The early part of the day was devoted to technology challenges. Obviously everyone did not say exactly the same things, and had a little bit of a different spin depending on what business they are in. But there was a lot of commonality between Intel, IBM, Xilinx… Read More

Xilinx, the University of FPGA

More than ever, FPGA training is the key to success. Which is why Xilinx, provides free, no charge video’s that can speak to the seasoned FPGA designer or to the interested community. These Videos are not like your high school graduation taped by Uncle Frank. These are detailed, professionally edited Xilinx Videos that will give… Read More

Structured Asic Dies…Again

There has always been a dream that you could do a design in a cheap easy to design technology and then, if the design was a hit, press a button and instantly move it into a cheaper unit-price high volume design. When I was at VLSI in the 1980s we had approaches to make it easy to move gate arrays (relatively large die area) into standard cells… Read More

Get into a Xilinx FPGA for Under $90

Jump into Xilinx Programmable Logic today! I wanted to encourage my dear readers if you have not tried using an Xilinx FPGA (Field Programmable Gate Array) or even CPLD (Complex Programmable Logic Device) then it is worth your time to begin your evaluation. Maybe you got one for Christmas? If not, it is easier than you think to start… Read More

Xilinx Pulls Back the 20nm UltraScale Curtain

This week Xilinx has announced that “The Xilinx 20nm All Programmable UltraScale™ portfolio is now available with detailed device tables, product documentation, design tools and methodology support.”

Do you know what 20nm is? It’s small, tiny. Think about it this way, as I just learned today that one nanometer is about as long… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center