As the largest FPGA vendor, Xilinx is on top of it’s social media game by using multiple channels to talk with customers and listen. Browsing their Home page I quickly found an RSS (Really Simple Syndication) icon just below the rotating banner images, plus a link to their Blog.… Read More

ASICs for Bitcoin Mining!

One of the hottest areas for Application Specific Integrated Circuits today is Bitcoin mining. A good friend of mine has a son who is involved in a Bitcoin start-up so we have been discussing this at great length and I will share what I have learned thus far. Coincidently, my wife asked me about Bitcoin during our most recent walk down… Read More

Xilinx Begins Shipping TSMC 20nm FPGAs!

Xilinx just announced the shipment of the first TSMC based 20 nm FPGAs, beating Altera to the punch yet again. Xilinx was also the first to ship TSMC 28nm FPGAs and will undoubtedly beat Altera to 14nm which could be the knockout punch we have all been waiting for. The Xilinx UltraScale is a new family of FPGAs that will use 20nm and 16nm… Read More

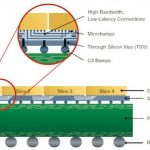

Xilinx and TSMC: Volume Production of 3D Parts

A couple of weeks ago, Xilinx and TSMC announced the production release of the Virtex-7 HT family, the industry’s first heterogeneous 3D ICs in production. With this milestone, all Xilinx 28nm 3D IC families are now in volume production. These 28nm devices were developed on TSMC’s Chip-on-Wafer-on-Substrate (CoWoS)… Read More

I could show you the FPGA, but then I’d have to configure you

One of the present ironies of the Internet of Things is as it seeks to connect every device on the planet, we are still designing those things with largely unconnected EDA tools. We may share libraries and source files on a server somewhere, but that is just the beginning of connection.

It is not surprising that synthesis tools from… Read More

Pigs Fly. Altera Goes with ARM on Intel 14nm

Altera announced in February that they would be using Intel as a foundry at 14nm. Historically they have used TSMC. Then in June they announced the Stratix 10 family of FPGAs that they would build on the Intel process. At the Globalpress summit in May I asked Vince Hu about their processor strategy. Here is what I wrote about itat the… Read More

Always-on Context-aware Sensors in Your Phone

Smartphones are smart but they are about to get smarter. The next big thing in mobile phones is to have a rich sensor environment: proximity, temperature and humidity, atmospheric pressure, light color, cover, gyroscope, magnetometer, accelerometer, ambient light, gesture and more. Some of these are already here, of course,… Read More

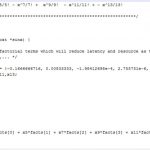

Xilinx’s Vivado HLS Will Float Your FPGA

Very rarely does the FPGA designer, especially with respect to RADAR, think of the FPGA as a floating point processor. Just to be sure I asked my 6 year old and she agreed. But you know what, the Xilinx FPGAs float. Go try it, order some up and fill up the tub.

Anyways I purpose a duel to the avid VHDL coder. I want you to design me a Sine(x) … Read More

Xilinx At 28nm: Keeping Power Down

Almost without exception these days, semiconductor products face strict power and thermal budgets. Of course there are many issues with dynamic power but one big area that has been getting increasingly problematic is static power. For various technical reasons we can no longer reduce the voltage as much as we would like from one… Read More

FPGAs The Life Savers

Silicon dominates our lives, CPU’s, GPU’s are in the limelight but the unsung hero is the FPGA. They simply do the work where other silicon dare not tread, as they are unfit for the task. Never send a boy to do a man’s job.

For a moment, if we can, just for a few minutes perhaps we can break away from the social media bubble… Read More

Solving the EDA tool fragmentation crisis