You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 89

[name] => FinFET

[slug] => finfet

[term_group] => 0

[term_taxonomy_id] => 89

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 231

[filter] => raw

[cat_ID] => 89

[category_count] => 231

[category_description] =>

[cat_name] => FinFET

[category_nicename] => finfet

[category_parent] => 0

[is_post] =>

)

If you plan on visiting Solido (the world leader in EDA software for variation-aware design of integrated circuits) at the Design Automation Conference next month for a demonstration of Variation Designer, register online now and get an autographed copy of “Mobile Unleashed”. Such a deal!

Solido Variation Designer is used by… Read More

Being that TSMC and Solido are founding members of SemiWiki, you should be able find out everything you ever wanted to know on their respective landing pages. If not, just ask a question in the SemiWiki forum and I can assure you it will be answered in great detail. And here are some other interesting 2015 factoids from Solido:… Read More

More than 500 designers (562) have responded to a survey made in 2015 by Synopsys. Answering to the question “What is the fastest clock speed of your design?” 56% have mentioned a clock higher than 500 MHz (and still 40% higher than 1 GHz). If you compare with the results obtained 10 years ago, the largest proportion of answers was for… Read More

Samsung Foundry had an intimate gathering recently for 200 customers and partners that I missed, but I know several people who attended. This event was a precursor to #53DAC where Samsung has the largest foundry presence. I was able to clarify what I had heard via a phone call with Kelvin Low so here is my version of what is important:… Read More

At SemiWiki we’ve been blogging for several years now on the semiconductor design challenges of FinFET technology and how it requires new software approaches to help chip designers answer fundamental questions about timing, power, area and design closure. When you mention the phrase Static Timing Analysis (STA) probably… Read More

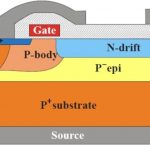

Process and device engineers are some of the unsung heroes in our semiconductor industry that have the daunting task of figuring out how to actually create a new process node that will fit some specific, market niche with sufficient yield to make their companies profitable and stand out from the competition. One such market segment… Read More

The intricacies of analog IP circuit design have always required special consideration during physical layout. The need for optimum device and/or cell matching on critical circuit topologies necessitates unique layout styles. The complex lithographic design rules of current FinFET process nodes impose additional restrictions… Read More

TSMC recently held their annual Technology Symposium in San Jose, a full-day event with a detailed review of their semiconductor process and packaging technology roadmap, and (risk and high-volume manufacturing) production schedules.… Read More

It is that time again, time for the originators of the pure-play foundry business to update their top customers and partners on the latest process technology developments and schedules. More specifically, all of the TSMC FinFET processes (16nm, 10nm, 7nm, and beyond), TSMC IP portfolio (CMOS image sensor, Embedded Flash, Power… Read More

Evolving opportunities call for new and improved solutions to handle data, bandwidth and power. Moving forward, what will be the high-growth applications that drive product and technology innovation? The CAGRs for smartphone and data center continue to be very strong and healthy. … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center