At a recent outing with FPGA friends from days gone by, the long running Xilinx vs Altera debate has come to an end. The bottom line is that Xilinx has used the FUD (fear, uncertainty, and doubt) of the Intel acquisition quite effectively against Altera and is racking up 20nm and 16nm design wins at an alarming rate. It will be a while … Read More

IC Designers talk about 28nm to 7nm challenges at #53DAC

IC design challenges are different at advanced nodes like 7nm, so to learn more about the topic I attended a panel luncheon at DAC sponsored by Cadence. The moderator was both funny and technically astute, quite the rare combination, so kudos to Professor Rob Rutenbar, a former Neolinear guy now at the University of Illinois. Panelists… Read More

NVIDIA GeForce GTX 1080 Poised To Claim The Gaming And VR Performance Crown

NVIDIA has been teasing the promise of Pascal for years, but this year Pascal’s performance became much more real. With the announcement of the Tesla P100 based on Pascal, NVIDIA was able to show the neural-network world what Pascal was really capable of. However, that chip is very different from the gaming-focused Pascal chip … Read More

IMEC Technology Forum (ITF) – Secrets of Semiconductor Scaling

IMEC is a technology research center located in Belgium that is one of the premier semiconductor research centers in the world today. The IMEC Technology Forum (ITF) is a two-day event attended by approximately 1,000 people to showcase the work done by IMEC and their partners.… Read More

Electrostatic Discharge analysis of FinFET technology

Sofics recently had the opportunity to characterize FinFET technology through cooperation with one of its customers. We analyzed the technology related to ESD and identified several challenges.… Read More

IMEC Technology Forum (ITF) – Moving the Electronics Industry Forward

IMEC is a technology research center located in Belgium that is one of the premier semiconductor research centers in the world today. The IMEC Technology Forum (ITF) is a two-day event attended by approximately 1,000 people to showcase the work done by IMEC and their partners.

Gary Patton is the Chief Technical Officer and Senior… Read More

TSMC Update at #53DAC!

TSMC is having an interesting year for sure. I was at the TSMC Symposium in Hsinchu last week and everyone was talking about the new 16FFC process. Silicon is out and it is exceeding expectations leading some people (me included) to believe that TSMC 16FFC will be the next TSMC 28nm in regards to popularity. To be clear, 16FFC is currently… Read More

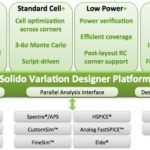

How TSMC Tackles Variation at Advanced Nodes

The design community is always hungry for high-performance, low-power, and low-cost devices. There is emergence of FinFET and FDSOI technologies at ultra-low process nodes to provide high-performance and low-power requirements at lower die-size. However, these advanced process nodes are prone to new sources of variation.… Read More

ARM tests out TSMC 10FinFET – with two cores

About 13 months ago, the leak blogs posted news of “Artemis” on an alleged ARM roadmap slide, supposedly a new 16FF ARM core positioned as the presumptive successor to the Cortex-A57. Now, we’re finding out what “Artemis” may actually be, inside a multi-core PPA test chip on TSMC 10FinFET.… Read More

IMEC Technology Forum (ITF) – IC Innovation

IMEC is a technology research center located in Belgium that is one of the premier semiconductor research centers in the world today. The IMEC Technology Forum (ITF) is a two-day event attended by approximately 1,000 people to showcase the work done by IMEC and their partners.

Luc Van Den Hove is the president and CEO of IMEC and he… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center