In electronic system design, we have grown comfortable with the idea that different regimes of analysis, such as the chip, the package and the system, or electrical, thermal and stress are more or less independent – what starts in one regime stays in that regime, give or take some margin information passed onto other regimes. And… Read More

FinFET ASICs for Networking, Data Center, AI and 5G

On the heels of successful seminars in Tokyo and Shanghai, eSilicon is starting the new year back in the cloud with a webinar version of the live events for those, like myself, who could not attend. The webinar will compress the 3 hour live event into 60 minutes which will provide a great place to start a conversation on your next chip… Read More

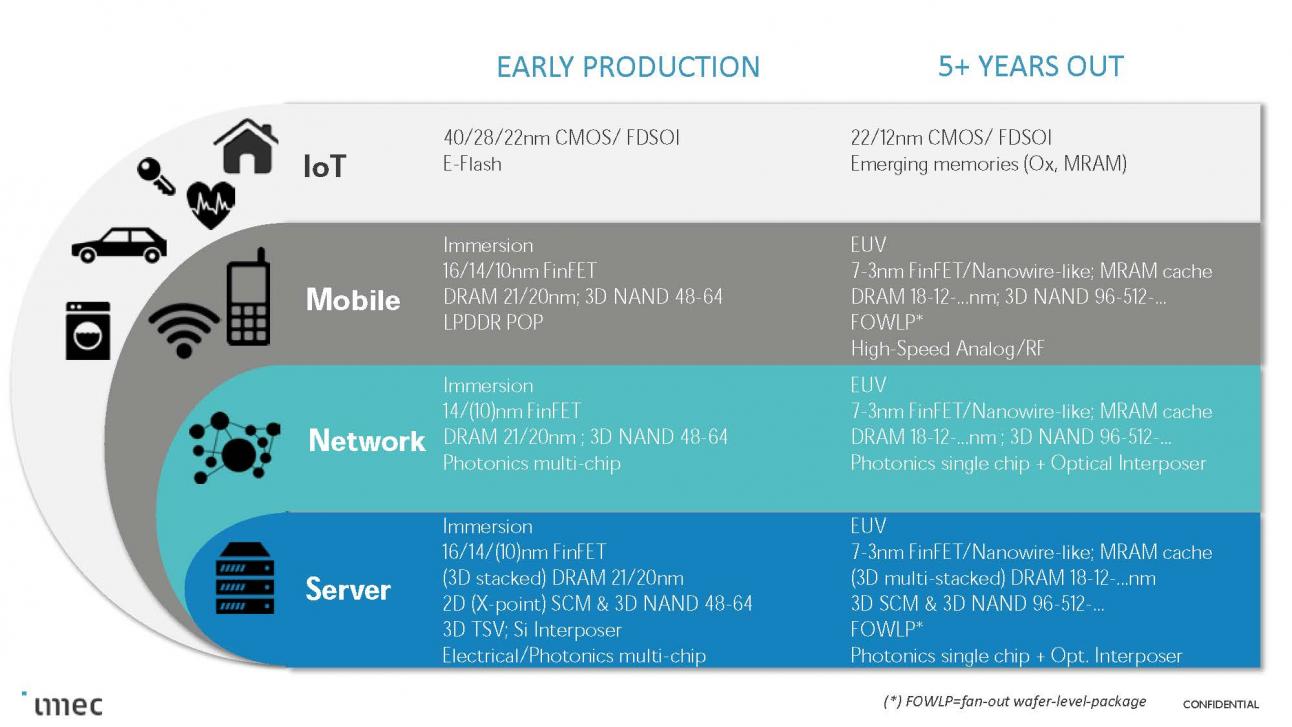

IEDM 2017 – imec Charting the Future of Logic

At the IEDM 2017, imec held an imec technology forum and presented several papers, I also had the opportunity to interview Anda Mocuta director of technology solutions and enablement. In this article I will summarize the keys points of what I learned about the future of logic. I will follow this up with a later article covering memory.… Read More

IEDM 2017 – Intel Versus GLOBALFOUNDRIES at the Leading Edge

As I have discussed in previous blogs, IEDM is one of the premier conferences to learn about the latest developments in semiconductor technology. … Read More

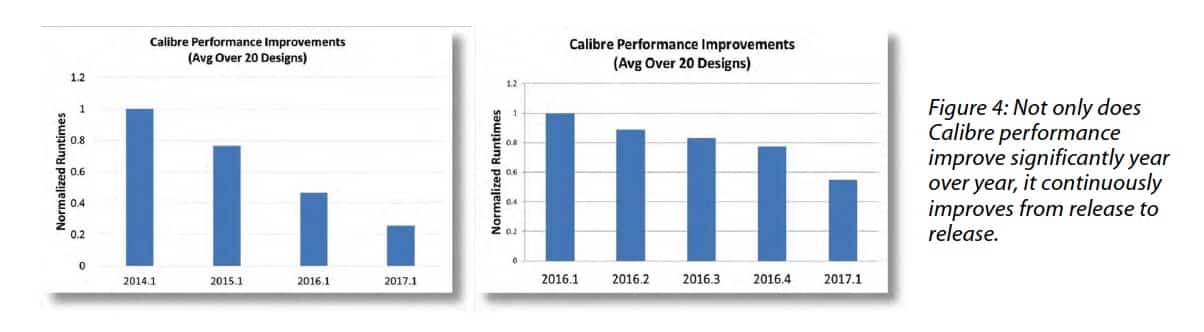

High Calibre Development Keeps Mentor on Top of the Game

One might be tempted to think that technology driven gains in computer performance might be enough to keep up with the needs of design and verification tools. We know that design complexity is increasing at a rate predicted by Moore’s Law. We also know that the performance of the computers used during IC development benefit from … Read More

Advanced ASICs – It Takes an Ecosystem

I remember the days of the IDM (integrated device manufacturer). For me, it was RCA, where I worked for 15 years as the company changed from RCA to GE and then ultimately to Harris Semiconductor. It’s a bit of a cliché, but life was simpler then, from a customer point of view at least. RCA did it all. We designed all the IP, did the physical… Read More

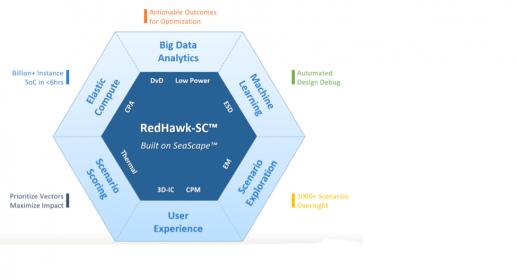

Big Data Analytics and Power Signoff at NVIDIA

While it’s interesting to hear a tool-vendor’s point of view on the capabilities of their product, it’s always more compelling to hear a customer/user point of view, especially when that customer is NVIDIA, a company known for making monster chips.

A quick recap on the concept. At 7nm, operating voltages are getting much closer… Read More

7nm SERDES Design and Qualification Challenges!

Semiconductor IP is the fastest growing market inside the fabless ecosystem, it always has been and always will be, especially now that non-traditional chip companies are quickly entering the mix. Towards the end of the year I always talk to the ecosystem to see what next year has in store for us and 2018 looks to be another year of … Read More

ASIC and TSMC are the AI Chip Unsung Heroes

One of the more exciting design start market segments that we track is Artificial Intelligence related ASICs. With NVIDIA making billions upon billions of dollars repurposing GPUs as AI engines in the cloud, the Application Specific Integrated Circuit business was sure to follow. Google now has its Tensor Processing Unit, Intel… Read More

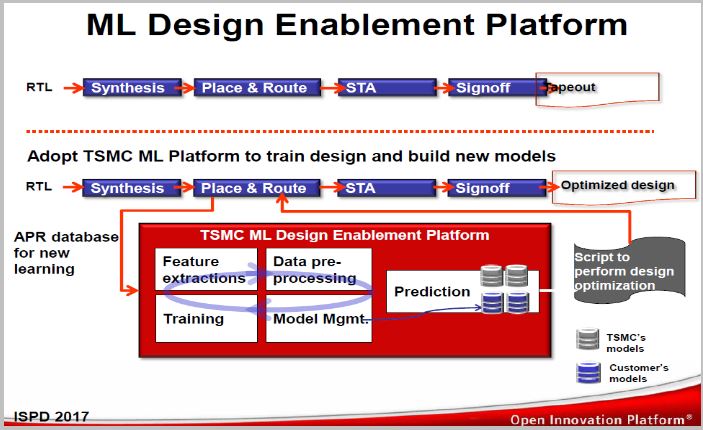

TSMC EDA 2.0 With Machine Learning: Are We There Yet ?

Recently we have been swamped by news of Artificial Intelligence applications in hardware and software by the increased adoption of Machine Learning (ML) and the shift of electronic industry towards IoT and automobiles. While plenty of discussions have covered the progress of embedded intelligence in product roll-outs, an… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center