You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 159

[name] => Siemens EDA

[slug] => siemens-eda

[term_group] => 0

[term_taxonomy_id] => 159

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 828

[filter] => raw

[cat_ID] => 159

[category_count] => 828

[category_description] =>

[cat_name] => Siemens EDA

[category_nicename] => siemens-eda

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 159

[name] => Siemens EDA

[slug] => siemens-eda

[term_group] => 0

[term_taxonomy_id] => 159

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 828

[filter] => raw

[cat_ID] => 159

[category_count] => 828

[category_description] =>

[cat_name] => Siemens EDA

[category_nicename] => siemens-eda

[category_parent] => 157

[is_post] =>

)

I was talking recently to Dina Medhat, a senior technical marketing engineer at Mentor, about, of all things, IO rings. It has not occurred to me that verifying that your IO rings comply with foundry rules presents new challenges.

IO ring checking isn’t new, nor is it unique to advanced IC process nodes. However, the same forces of… Read More

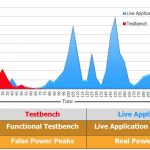

On your last SoC project how well did your dynamic power estimates match up with silicon results, especially while running real applications on your electronic product? If your answer was, “Well, not too good”, then keep reading this blog. A classical approach to dynamic power analysis is to run your functional testbench… Read More

Silicon Photonics is the hottest prospect for blazing fast communication between chips in servers, data centers, and supercomputers.

By using light instead of electrical signals, it promise to usher in a new standard of high performance, low power devices while extending the use of more mature process nodes, helping to reduce… Read More

It’s less than four weeks to go at DAC 2015 and the program is final now. So I started investigating new technologies, trends, methodologies, and tools that will be unveiled and discussed in this DAC. In the hindsight of the semiconductor industry over the last year, I see 14nm technologies in the realization stage and 10nm beckoning… Read More

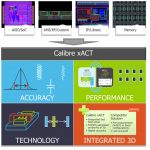

Mentor Graphics made a big announcement regarding SOC extraction at their User2User conference in San Jose during April. Before I get to the meat of the announcement, I’d like to reflect back on the early days of Calibre-DRC at Mentor. I was in Sales at Mentor around 1999, and Calibre-DRC was the new kid on the block. We had to go convince… Read More

If you’ve been following DAC general chair Anne Cirkel’s weekly blog, you know the conference program is now final. There’s much to suggest it will be a great DAC, including a record number of submissions in several content categories and a compelling lineup of keynoters. The week will start with an update on Google’s smart contact… Read More

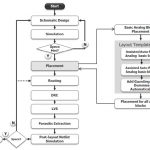

Digital IC design has been largely automated with high-level languages, RTL coding, logic synthesis, and automated place and route tools. What about analog IC layout automation, is it possible? A few EDA companies think that it is possible and even practical. In recent memory there were two companies really focused on analog … Read More

Yesterday was the Mentor users’ group U2U. As usual, Wally Rhines gave the keynote, this year entitled Secure Silicon, Enabler for the Internet of Things. Wally started off saying it was a challenge to find a new angle. The number of news articles on cloud computing has exploded from nothing to 72,000 last year. On IoT from … Read More

The use of silicon interposers is growing. Several years ago Xilinx broke new ground by employing interposers in their Virtex®-7 H580T FPGA. Last August Samsung announced what they say is the first DDR4 module to use 3D TSV’s for enterprise servers. Their 64GB double data rate-4 modules will be used for high end computing where … Read More

Mentor Graphics’ User2User conference will be held next week on April 21[SUP]st[/SUP] at the San Jose DoubleTree Hotel. This one-day, free conference is the perfect opportunity to learn, network, and share with other Mentor Graphics users.

The day starts off with back-to-back keynotes that examine different aspects of the … Read More