You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4439

[filter] => raw

[cat_ID] => 157

[category_count] => 4439

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

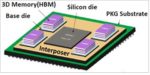

3D-ICs bring together multiple silicon dies into a single package that’s significantly larger and complex than traditional systems on a chip (SoCs). There’s no doubt these innovative designs are revolutionizing the semiconductor industry.

3D-ICs offer a variety of performance advantages over traditional SoCs. Because … Read More

Cadence Execs Look to the Futureby Dave Bursky on 07-01-2022 at 6:00 amCategories: Cadence, EDA, Events

Everything is becoming digital, and everything digital requires semiconductors. Cadence’s President and CEO, Dr. Anirudh Devgan, highlighted this at the recent CadenceLIVE user conference and discussed many of the company’s accomplishments and future directions. Dr. Devgan also sees the emergence of data—especially … Read More

The ESD Alliance collects and reports every quarter the revenue trends for both EDA and Semiconductor IP (SiP), and the biggest component for the past few years has been the SiP, as IP re-use dominates new designs. For Q4 of 2021 the total SiP revenue was $1,314.3 Million, enjoying a 24.8% growth in just one year. Here’s a chart… Read More

Recently, in one of my regular check-ins with AMIQ EDA, I was pleased that they linked me up with an active customer. The resulting post summarized my discussion with three engineers from Kepler Communications Inc. They talked about using one of the AMIQ EDA products in the design of FPGAs for space-borne Internet connectivity.… Read More

Artificially stalling datapaths and virtual channels is a creative method to uncover corner case timing bugs. A paper from Nvidia describes a refinement to this technique. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue… Read More

Semiconductor manufacturers are under constantly increasing and intense pressure to accelerate innovative new chip designs to market faster than ever in smaller package sizes while assuring signal integrity and reducing power consumption. Three-dimensional integrated circuits (3D-ICs) promise to answer all these demands… Read More

Our laptops and desktop computers have billions of transistors in their application processor chips, yet I often don’t consider the reliability effects of aging that the transistors experience in the chips. At the recent Synopsys User Group (aka SNUG), there was a technical presentation on this topic from Srinivas Bodapati,… Read More

I’ve written several articles on High-Level Synthesis (HLS), designing in C, C++ or SystemC, then synthesizing to RTL. There is unquestionable appeal to the concept. A higher level of abstraction enables a function to be described in less lines of code (LOC). Which immediately offers higher productivity and implies less bugs… Read More

For many decades now, modern optical technology has been deployed in networking infrastructure, for long haul and medium haul links to support internet communications. The foundation of this technology is photonics, which is the science of generation, manipulation and detection of light for performing functions otherwise… Read More

I wrote recently about Siemens EDA’s philosophy on designing quality in from the outset, rather than trying to verify it in. The first step is moving up the level of abstraction for design. They mentioned the advantages of HLS in this respect and I refined that to “for DSP-centric applications”. A Stanford group recently presented… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center