A Petri nets blog scored highest in engagement last year. This month we review application of the technique to validating an expanding range of JEDEC memory standards. Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue… Read More

Electronic Design Automation

How to Enable High-Performance VLSI Engineering Environments

Very Large Scale Integration (VLSI) engineering organizations are known for their intricate workflows that require high-performance simulation software and an abundance of simulation licenses to create cutting-edge chips. These workflows involve complex dependency trees, where one task depends on the completion of another… Read More

Synopsys Accelerates First-Pass Silicon Success for Banias Labs’ Networking SoC

Banias Labs is a semiconductor company that develops infrastructure solutions for next-generation communications. Its target market is the high-performance computing infrastructure market including hyperscale data center, networking, AI, optical module, and Ethernet switch SoCs for emerging high-performance computing… Read More

More Software-Based Testing, Less Errata

In verification there is an ever-popular question, “When can we stop verifying?” The intent behind the question is “when will we have found all the important bugs?” but the reality is that you stop verifying when you run out of time. Any unresolved bugs appear in errata lists delivered with the product (some running to 100 or more … Read More

S2C Helps Client to Achieve High-Performance Secure GPU Chip Verification

S2C, a leading provider of FPGA-based prototyping solutions, has helped a client achieve high-performance secure GPU chip verification. With the help of S2C’s Prodigy prototyping solution, the client was able to start software development and hardware-software co-design early, leading to accelerated time-to-market… Read More

What’s New with Cadence Virtuoso?

It was back in 1991 that Cadence first announced the Virtuoso product name, and here we are 32 years later and the product is alive and doing quite well. Steven Lewis from Cadence gave me an update on something new that they call Virtuoso Studio, and it’s all about custom IC design for the real world. In those 32 years we’ve… Read More

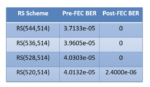

Mitigating the Effects of DFE Error Propagation on High-Speed SerDes Links

As digital transmission speeds increase, designers use various techniques to improve the signal-to-noise ratio at the receiver output. One such technique is the Decision Feedback Equalizer (DFE) scheme, commonly used in high-speed Serializer-Deserializer (SerDes) circuits to mitigate the effects of channel noise and … Read More

AI Assists PCB Designers

Generative AI is all the rage with systems like ChatGPT, Google Bard and DALL-E being introduced with great fanfare in the past year. The EDA industry has also been keen to adopt the trends of using AI techniques to assist IC engineers across many disciplines. Saugat Sen, Product Marketing at Cadence did a video call with me to explain… Read More

Multi-Die Systems: The Biggest Disruption in Computing for Years

At the recent Synopsys Users Group Meeting (SNUG) I had the honor of leading a panel of experts on the topic of chiplets. The discussion was based on a report published by the MIT Technology Review Insights in cooperation with Synopsys. This is a very comprehensive report (12 pages) that is available online HERE.

Here is the preface… Read More

Hardware Root of Trust for Automotive Safety

Traveling by car is something that I take for granted and I just expect that my trips will be safe, yet our cars are increasingly using dozens of ECUs, SoCs and millions of lines of software code that combined together present a target for hackers or system failures. The Automotive Safety Integrity Levels (ASIL) are known by the letters:… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry