Anna has more than 25 years of expertise in managing complex R&D organizations and programs, giving birth to a number of innovative EDA technologies. She has pioneered the study and development of several generations of IC and package co-design environments and has held senior positions at leading semiconductor and EDA … Read More

Electronic Design Automation

Sirius Wireless Partners with S2C on Wi-Fi6/BT RF IP Verification System for Finer Chip Design

Sirius Wireless, a provider of RF IP solutions, collaborated with FPGA prototyping solutions expert S2C to develop its Wi-Fi6/BT RF IP Verification System, aiming to improve work efficiency and reduce time-to-market for their clients.

The emergence of Wi-Fi6, a wireless connection technology (WCT), has unleashed unexpected… Read More

Next-Gen AI Engine for Intelligent Vision Applications

Artificial Intelligence (AI) has witnessed explosive growth in applications across various industries, ranging from autonomous vehicles and natural language processing to computer vision and robotics. The AI embedded semiconductor market is projected to reach $800 billion by year 2030. Compare this with just $48 billion… Read More

VC Formal Enabled QED Proofs on a RISC-V Core

The Synopsys VC Formal group have a real talent for finding industry speakers to talk on illuminating outside-the-box-topics in formal verification. Not too long ago I covered an Intel talk of this kind. A recent webinar highlighted use of formal methods used together with a cool technique I have covered elsewhere called Quick… Read More

Insights into DevOps Trends in Hardware Design

Periodically I like to check in on the unsung heroes behind the attention-grabbing world of design. I’m speaking of the people responsible for the development and deployment infrastructure on which we all depend – version control, testing, build, release – collectively known these days as DevOps (development operations). … Read More

Breakthrough Gains in RTL Productivity and Quality of Results with Cadence Joules RTL Design Studio

Register Transfer Level (RTL) is a crucial and valuable concept in digital hardware design. Over the years, it has played a fundamental role in enabling design of complex digital chips. By abstracting away implementation details and providing a clear description of digital behavior, RTL has contributed significantly to the… Read More

Cadence and AI at #60DAC

Paul Cunningham from Cadence presented at the #60DAC Pavilion and gave one of the most optimistic visions of AI applied to EDA that I’ve witnessed, so hopefully I can convey some of his enthusiasm and outright excitement in my blog report. Mr. Cunningham reviewed the various ages of EDA design with each era providing about… Read More

Qualitative Shift in RISC-V Targets Raises Verification Bar

I had grown comfortable thinking about RISC-V as a cost-saving and more flexible alternative to Intel/AMD or Arm in embedded applications. Where clearly it is already doing very well. But following a discussion with Dave Kelf and Adnan Hamid of Breker, RISC-V goals have become much more ambitious, chasing the same big system applications… Read More

Automated Code Review. Innovation in Verification

A little thinking outside the box this time. Microsoft is adding automation to their (and LinkedIn) code reviews; maybe we should consider this option also? Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series… Read More

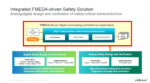

Xcelium Safety Certification Rounds Out Cadence Safety Solution

While fully autonomous driving may now be a distant dream, ADAS continues to be a very active industry driver as much for its safety advantages as for other features. Today in the hierarchy of SAE levels, SAE 2+ may represent the most active area of development rather than levels 3 through 5. This range of options still requires a human… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry