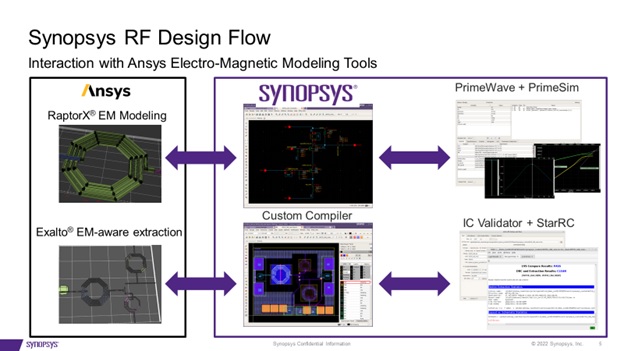

The design and characterization of RF circuits is a complex process that requires an RF designer to overcome a variety of challenges. Not only do they face the complexities posed by advanced semiconductor processes and the need to meet the demanding requirements of modern wireless standards, designers must also account for electromagnetic effects that become significant at RF and mmWave frequencies. The Synopsys Custom Design Family provides a holistic solution to RF design challenges, including accurate EM modeling with industry-leading tools such as the Ansys EM Tool suite, simulation and analysis of important RF measurements, productive layout creation, and RC extraction and physical verification with foundry qualified signoff tools.

What you will Learn

In this webinar we will use a Low Noise Amplifier design to illustrate the steps needed for creating state-of-the-art RF circuits. We will start with Synopsys Custom Compiler for design creation, simulation and results analysis. Next we will perform inductor synthesis with the Ansys VeloceRF tool and Inductor modeling with Ansys RaptorX . The next step will be to create a layout with Custom Compiler Layout Editor. Once the layout is complete, we will perform physical verification and parasitic extraction with IC Validator and StarRC and use Ansys Exalto for EM extraction of the critical nets. As a final step we will simulate the combined extracted model with the PrimeSim SPICE simulator for post-layout verification and analyze the results in PrimeWave Design Environment.

The Synopsys Custom Design Family is a complete front to back solution for all types of custom integrated circuit design. It includes Custom Compiler, a modern and productive editor for schematics and layout, the PrimeSim Continuum simulation solution for fast and accurate analog and RF simulation, and the PrimeWave Design Environment for post-processing and viewing of simulation results. It also features natively integrated signoff tools – Star RC extraction and IC Validator physical verification.

A wide variety of third-party tools are integrated with the Synopsys custom design platform, including the Ansys tools for Electro Magnetic modeling and extraction, which will be featured in this webinar.

The Presenters

Samad Parekh

Product Marketing Manager, Sr. Staff

Synopsys

Samad Parekh is the Product Manager for Spice Simulation and Design Environment products at Synopsys. He has 10 years of experience serving as a senior member of the Synopsys Applications Engineering team supporting Analog and Custom tools. Prior to Synopsys, Samad worked as an RF designer for 6 years designing RF and microwave circuits for the cellular and aerospace markets. Samad holds a BSEE from UCLA and MSEE from UC Irvine.

Kelly Damalou

Product Manager

Ansys

Kelly Damalou is Product Manager for the Ansys on-chip electromagnetic simulation portfolio. For the past 20 years she has worked closely with leading semiconductor companies, helping them address their electromagnetic challenges. She joined Ansys in 2019 through the acquisition of Helic, where, since 2004 she held several positions both in Product Development and Field Operations. Kelly holds a diploma in Electrical Engineering from the University of Patras, Greece, and an MBA from the University of Piraeus, Greece.

To Learn More

Please register for the webinar below:

Also read:

DSP IP for High Performance Sensor Fusion on an Embedded Budget

Intelligently Optimizing Constrained Random

Using STA with Aging Analysis for Robust IC Designs

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.