I just did a Google search for “3D IC”, and was stunned to see it return a whopping 476,000 results. This topic is trending, because more companies are using advanced IC packaging to meet their requirements, and yet the engineers doing the 3D IC design have new challenges to overcome. One of those challenges is creating… Read More

Electronic Design Automation

UCIe Specification Streamlines Multi-Die System Design with Chiplets

Over the last few years, the design of application-specific ICs as well as high-performance CPUs and other complex ICs has hit a proverbial wall. This wall is built from several issues: first, chip sizes have grown so large that they can fill the entire mask reticle and that could limit future growth. Second, the large chip size impacts… Read More

Methodology to Minimize the Impact of Duty Cycle Distortion in Clock Distribution Networks

Synchronous circuits dominate the electronic world because clocking eases the design of circuits compared to asynchronous circuits. At the same time, clocking also introduces its share of challenges to overcome. No wonder, a tremendous amount of time and effort have been spent over the years on developing and implementing … Read More

Semifore is Supplying Pain Relief for Some World-Changing Applications

In a recent post, I discussed how Samtec is fueling the AI revolution. In that post, I talked about how smart everything seems to be everywhere, changing the way we work, the way we think about our health and ultimately improving life on the planet. These are lofty statements, but the evidence is growing that the newest wave of applications… Read More

Load-Managing Verification Hardware Acceleration in the Cloud

There’s a reason the verification hardware accelerator business is growing so impressively. Modern SoCs – now routinely multi-billion gate devices – must be verified/validated against massively demanding test plans, requiring high levels of test coverage. Use cases extend all the way up to firmware, OSes, even application… Read More

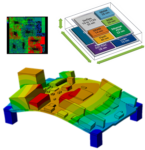

Ansys’ Emergence as a Tier 1 EDA Player— and What That Means for 3D-IC

Over its 40+ year history, electronic design automation (EDA) has seen many companies rise, fall, and merge. In the beginning, in the 1980s, the industry was dominated by what came to be known as the big three — Daisy Systems, Mentor Graphics, and Valid Logic (the infamous “DMV”). The Big 3 has morphed over the years, eventually settling… Read More

Finally, A Serious Attack on Debug Productivity

Verification technologies have progressed in almost all domains over the years. We’re now substantially more productive in creating tests for block, SoC and hybrid software/hardware verification. These tests provide better coverage through randomization and formal modeling. And verification engines are faster – substantially… Read More

Advanced EM simulations target conducted EMI and transients

A vital benefit of advanced EM simulations is their ability to take on complicated physical test setups, substituting far easier virtual tests yielding accurate results earlier during design activities. The latest release of Keysight PathWave ADS 2023 continues speeding up engineering workflows. Let’s look at three… Read More

Three Ways to Meet Manufacturing Rules in Advanced Package Designs

Often designers are amazed at the diversity of requirements fabricators and manufacturers have for metal filled areas in advanced package designs. Package fabricators and manufacturers do not like solid metal planes or large metal areas. Their strict metal fill requirements address two main issues. The dielectric and metal… Read More

Synopsys Vision Processor Inside SiMa.ai Edge ML Platform

SiMa.ai just announced that they achieved first silicon success on their new MLSoC, for AI applications at the edge, using Synopsys’ design, verification, IP and design services solutions. Notably this design includes the Synopsys ARC® EV74 processor (among other IP) for vision processing. SiMa.ai claim their platform, now… Read More

Should Intel be Split in Half?