Kathryn Kranen, CEO of Jasper was elected chairman of EDAC for 2012-2014. She has has 20 years EDA industry. She started her career as a design engineer at Rockwell International and then joined Daisy Systems (one of the DMV, the second generation of EDA companies). She then moved to be VP of North American sales at Quickturn (emulation)… Read More

Electronic Design Automation

BDA TSMC Theater Presentation

I caught the Berkeley Design Automation presentation in the TSMC Theater, where Simon Young (BDA’s director of product marketing) described the Analog FastSPICE (AFS) nanometer circuit verification platform, built on their foundation of very fast, very accurate, high capacity circuit simulation.

BDA claims the AFS platform… Read More

Ausdia’s Timevision

I met Sam Appleton of Ausdia during DAC. I found it quite hard to understand exactly what they do. I’ve talked before about something that I nick-named City Slickers’ Marketing. It is named after the following exchange from the movie City Slickers:Curly: Do you know what the secret of life is? [holds up one finger] This.… Read More

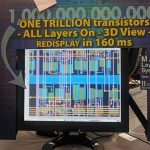

One Billion Transistor IC Layout Editing

There are only a handful of billion transistor IC designs in existence today, so when an EDA company touts 1 trillion transistor IC layout editing then I take notice. This year at DAC I met with Katherine Hayes and Karen Mangum of Micro Magic to get an update on their IC layout tools.… Read More

From SPICE Netlist back to Schematics at DAC

I first heard about SPICE Vision Pro when working at Mentor Graphics where we needed a way to visualize SPICE netlists and debug SPICE simulation results node by node on a design where we didn’t have the original schematics. Last Monday I met the engineers from Concept Engineering in their booth at DAC to get an update, Gerhard… Read More

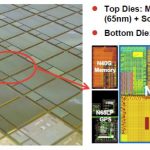

Cadence/TSMC 3D

Mark Twain remarked that everyone talks about the weather but nobody does anything about it. 3D ICs seems to be a bit like that. Over the last couple of years there have been lots of people talking about 3D but very little that has actually been manufactured. In addition to the weather, everyone talks about Xilinx’s 3D Virtex… Read More

Fast SPICE from Kiev at DAC

Monday at DAC I met with an EDA start-up called Symica based in Kiev. Ian Tsybulkin, CEO met with me to give an overview of their tools.… Read More

A DAC Update from Mentor Graphics on IC Layout and Circuit Simulation Tools

Linda Fosler, Tom Daspit and Mitch from Mentor Graphics met with me last Monday at DAC to provide an update on IC layout and circuit simulation tools. My notes follow:

Overview – Pyxis for Schematic and Layout, IC Station is re-branded as Pyxis. (Pyxis schematic is still Falcon, Ample language is still used.)… Read More

ST using Cadence IC Tools with Module Generators

Cadence invited Francois Lemery of ST Microelectronics to speak at a luncheon last Monday at DAC about designing for the 20nm node using module generators. Here are my trip report notes:

Press at DAC

The way that the press that covers EDA has changed in the last few years is quite dramatic. Semiwiki is, of course, part of that change. The official press is less and less relevant and bloggers and newsletters are more and more important.… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior