Last month I blogged about CircuitLaband received some two dozen comments, so clearly there is keen interest in using web-based tools for electronic circuit design and using the cloud to save designs plus run simulations. Today I’m reporting on TINACloud, provided by a company called DesignSoft. … Read More

Electronic Design Automation

Who is One Step Above Colgate and One Below P&G?

So who do you think is #31 on the list on Forbes list of the most innovative companies in the world? One place above Colgate and one place below Procter and Gamble. Your first thought is probably why am I asking this on a blog covering semiconductors and going on about toothpaste manufacturers. The answer is Dassault Systèmes. Perhaps… Read More

Test, The Forgotten Step-Child of Semiconductor Design

Somehow, when designing a chip it is synthesis and place & route that gets all the attention. But it is no good taping out perfect layout without also having away to test the silicon. Somehow, test just isn’t as glamorous.

On September 10-12th is the International Test Conference which, as usual, is at the Disneyland Hotel… Read More

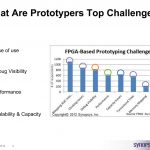

More to the story than bigger FPGA-based prototyping

Still not convinced on the value of FPGA-based prototyping systems, or using older technology? I’ve been trying to find the story beyond just bigger, badder FPGAs in a box that you pour RTL into – and found some hints in a webinar on the Synopsys HAPS-70 from earlier this year.… Read More

Atrenta Seminars in Asia – Making RTL Signoff Real

Engaging with the semiconductor ecosystem is critical to surviving in the fast paced times we work in. Face to face interaction at all levels is key and semiconductor IP is a prime example. How do you ensure that your IP meets objective quality requirements before integration into your SoC, and that your SoC is ready for handoff to… Read More

Why Adopt Hierarchical Test for SoC Designs

IC designers have been creating with hierarchy for years to better manage large design sizes, however for the test world the concept of hierarchy and emerging standards is a bit newer. TSMC and Synopsys jointly created a webinarthat addresses hierarchical test, so I’ve attended it this week and summarized my findings here.… Read More

Accelerating SoC Simulation Times

There never seems to be enough time in a SoC project to simulate all of the cycles and tests that you want to run, so any technique to accelerate each run is welcomed. You can just wait for your software-based RTL simulator to finish running, or you can consider using a hardware-based accelerator approach. I learned more about one such… Read More

Don’t Shoot Yourself in the Foot With Timing Exceptions

Timing exceptions are ways of guiding design tools, primarily synthesis and static timing analysis (STA), but these days also place & route and perhaps other tools. Most paths in a design go from one register to the next register. Both registers are on the same clock, and the design needs to ensure that the signal can make it from… Read More

Let’s Drive To Dearborn on 19th Sep….

[The VLC developed by Edison2, winner of the Progressive Automotive X-Prize]

Now that we have “The Very Light Car” of the world at more than 100 MPG!! Yes, this is the car developed by Edison2, one among the three winners of the Progressive Insurance Automotive X-Prize, a global competition; Edison2 won in the main stream class. … Read More

How to Benchmark a Processor

How do you benchmark a processor? It seems like it should be easy, just run some code and see how fast it is. Traditionally processors were indeed benchmarked by raw performance like GMACS, GFLOPS, memory bandwidth and so on. But in today’s world where systems have become very complex and applications very compute intensive, the… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?