Monday morning at DAC I met with Real Intent to get an update on their SoC sign-off tools:

- Dr. Prakash Narain, President and CEO

- Graham Bell, Sr. Dir. Mktg.

Years ago Prakash was at IBM the only two years that they attended DAC, in an attempt to offer their internal EDA tools to the EDA marketplace. Graham worked at Nassda marketing the HSIM hierarchical FastSPICE simulator, competing against me with Mentor’s Mach TA simulator (HSIM won, big time).

Dr. Prakash Narain, Graham Bell

Q: What EDA tools are you offering?

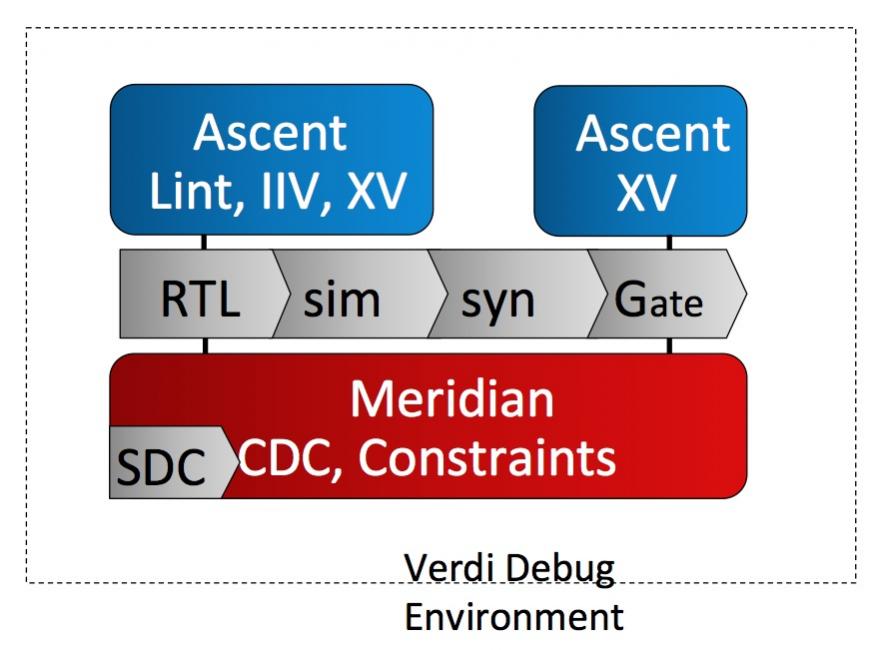

A: We’ve got two major EDA tools, ASCENT and MERIDIAN.ASCENT

-

[*=1]Lint

[*=1]Implied Intent Verification

[*=1]X-Verification

MERIDIAN

-

[*=1]CDC (Clock Domain Crossing)

[*=1]Constraints

Ascent (Lint) – Evaluation times are quick, about 450 million gates per hour. It’s so fast I only need a few copies for many projects. Training requirements are minimal. Can be configured and extended by users for their methodology.

Meridian (CDC) – An intense analysis process. Trying to integrate IP from many sources causes challenges. Evaluation has both benchmarking and training combined. Close support from AE to get the best initial results, then you become trained. Helps in IP qualification.

Q: How are SoC designers doing RTL today?

A: At the highest level they are using static tools where the use model has rules and checking, they look at their results, refine the tools settings, then continue to iterate until timing looks acceptable. This is not a very efficient model.

Q: How is your approach different?

A: Our tools have a very fast turn around per iteration, producing the fewest iterations with the least effort, highest capacity and best precision.

Q: What kind of SoC customers are using your tools?

A: We have customers in several segments: FPGA, GPU, CPU, DSP, mobile, networking.

Q: How are your tools different than Atrenta?

A: Atrenta has more legacy tools developed over the past 10 years, while our tools are newer and are more tuned. We are displacing older tools. Atrenta has a unified platform, all their tools are included as a bundle, however all of our tools are independent so you just get what you actually need.

Q: How is business for Real Intent?

A: We’ve seen a 70% bookings growth in 2013. Last year our revenue doubled, and we’re on track to do that again this year.

Q: What type of engineer uses ASCENT or MERIDIAN?

A: Engineers that are implementing the chip design.

Q: How do you get the highest capacity?

A: For our CDC tool the hierarchy is maintained for viewing results, but for analysis we use a flat approach so can handle 560 million gates at a time. You’ll need a workstation with lots of RAM to run this tool on large designs. The average SoC that we are now seeing has hundreds of millions of logic gates, the growth has been explosive.

Q: What kind of improvements should I expect to see by DAC in 2014?

A: For next year expect to see improvements in Constraints, X verification and reset analysis.

lang: en_US

Share this post via:

Solving the EDA tool fragmentation crisis