One of the first blogs I wrote on SemiWiki was on clock domain crossing (CDC). I thought it was rather a specialized subject, a sort of minority interest. It turned out to be one of the most-read blogs I’ve written. Modern SoCs have lots of unrelated clocks, maybe hundreds, and so ensuring that signals going from one clock domain… Read More

Electronic Design Automation

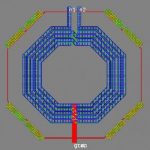

EM Solver and Visualization Essential for Device Design

In many designs, an on chip inductor is created as though it were simply a device with an L and a Q value. Of course this view would seem to make life simpler for designers and the tools they use. But in reality even a simple inductor is really a complex compound structure with many electromagnetic elements interacting in complex ways.… Read More

The Biggest Private EDA Company

I talked this morning with fellow Brit David Halliday. More importantly, he is CEO of Silvaco, which he thinks must be the biggest private EDA company in the world. He didn’t reveal their revenue numbers but they have around 250-300 people and are profitable so you can make your own estimate.

David became CEO when Ivan Pesic,… Read More

Analog & Mixed-Signal Design Lunch & Learn

I’m a big fan of lunch and learns, mainly because I’m a big fan of lunch but I also like to learn. I’m also a big fan of Tanner EDA which is why I helped organize this event. Face to face interaction amongst the fabless semiconductor ecosystem is critical to our success so stop on by and network, lunch is on me.

Take a look at the Brief History… Read More

New at DAC: IP, Automotive, Security

The deadline for panel sessions, workshops, tutorials and co-located conferences for DAC 2014 is October 21st. That’s next Monday!

DAC 2014 will not only focus on EDA and embedded systems and software but

also include:

- design methods for automotive systems and software

- hardware and embedded systems security

- IP (semiconductor

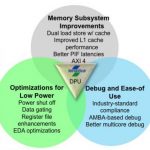

Putting the Ten in Tensilica

Chris Rowen of Cadence’s Tensilica announced the tenth generation of the Xtensa customizable processor at the Linley Microprocessor Conference yesterday. Chris was one of the founders of Tensilica…back in 1997. I believe that the first version was released in 1999. Over the years the Tensilica business changed.… Read More

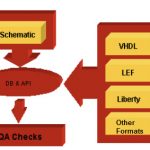

Semiconductor IP Library QA Just Got Easier

Imagine that you’re working in a CAD group and just received a new library of a few hundred IP blocks and you needed to know if these blocks conform to your design and quality standards. There are many questions about library and IP quality:

- Are all of the views consistent (layout, schematic, HDL, test, timing, SPICE)?

- Are there

How to Simplify Complexities in Power Verification?

With multiple functionalities added into a single chip, be it a SoC or an ASIC, maintaining low power consumption has become critical for any design. Various techniques at the technology as well as design level are employed to accomplish the low power target. These include thinner oxides in transistors, different sections of … Read More

Using HLS to Turbocharge Verification

One of the benefits of using high-level synthesis is obviously the ease of writing some algorithms in SystemC since it is at a higher level than RTL (that’s why we call it high-level synthesis!). But a second benefit is at the verification level. Since a lot of the verification gets done at the SystemC level, less needs to be done at … Read More

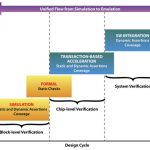

Assertions verifying blocks to systems at Broadcom

Speaking from experience, it is very difficult to get an OEM customer to talk about how they actually use standards and vendor products. A new white paper co-authored by Broadcom lends insight into how a variety of technologies combine in a flow from IP block simulation verification with assertions to complete SoC emulation with… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center