Once upon a time there was a struggle for verification completion of semiconductor designs at gate level. Today, beyond imagination, there is a struggle to verify a design with billions of gates at the RTL level which may never complete. The designs are large SoCs with complex architectures and several constraints of area, performance,… Read More

Electronic Design Automation

Taking a leap forward from TCAD

We all know that Technology Computer Aided Design (TCAD) simulations are essential in developing processes for semiconductor manufacturing. From the very nature of these simulations (involving physical structure and corresponding electrical characteristics of a transistor or device), they are predominantly finite-element… Read More

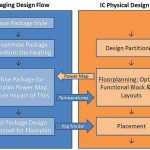

Temperature – The Fourth Aspect to Look at in SoC Design

In my career in semiconductor industry, I can recall, in the beginning there was emphasis on design completion with automation as fast as possible. The primary considerations were area and speed of completion of a semiconductor design. Today, with unprecedented increase in multiple functions on the same chip and density of the… Read More

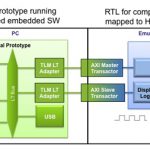

Hybrid Emulation

Hybrid emulation is when part of the system is run in the emulator and part of the system is run in a virtual prototype. Typically a model of the processor(s) is run in the virtual platform and then the rest of the design is modeled by running the RTL on the emulator. I talked to Tom Borgstrom at Synopsys about what technology they have … Read More

Power Modeling and Simulation of System Memory Subsystem

One great benefit of designing at the ESL level is the promise of power savings on the order of 40% to 70% compared to using an RTL approach. Since a typical SoC can contain a hierarchy of memory, this kind of power savings could be a critical factor in meeting PPA goals. To find out how an SoC designer could use such an ESL approach to power… Read More

Cadence Results: Good but Palladium under Price Pressure

Cadence announced their 2Q results this afternoon. I listened to the conference call.

You can read all the details of the results in the press release but the big picture is:

- Revenue $379K, net income $23M GAAP or $64M non-GAAP (8, 21c per share, beat estimates by 1c). Equivalent quarter last year was $362M so less than 5% increase)

Intel vs AMD

While listening to the Intel and AMD conference calls last week I was reminded of the ATI acquisition by AMD and the painfully long cultural assimilation that ensued. The title of this blog could just as easily have been “Custom vs Synthesizable Design Cultures” or “The Real Reason Why AMD is Fabless” because that is closer to how … Read More

When is a Million-Year MTBF Too Short?

The reliability metric, Mean Time Between Failures (MTBF), is often misunderstood. Use of an MTBF metric generally assumes a random failure process, one that is very infrequent and has no memory of past failures. Such failure modes can occur in System-on-Chip (SoC) designs and include radiation effects, synchronizer malfunctions… Read More

New Release of Semulator3D at #semiconwest

One of Coventor’s flagship products is SEMulator3D, and at Semicon West they announced a new version, 2014.100.

SEMulator3D is a powerful 3D semiconductor and MEMS process modeling platform. It uses highly efficient physics-driven voxel modeling technology. It models the physical effects of process steps, which is… Read More

Winds of Change in the Custom Chip Market

The most interesting part of the semiconductor market for me has always been the Custom Chip sector – the FPGA, ASIC and SoC companies where I have spent my entire career. These three segments provide an excellent barometer of the overall state of financial health and technological innovation for the entire High Tech industry, … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center