A recent comment by a DACattendee mentioned that the IoT acronym was so over-used as to make him get upset at EDA vendors that all purport to be enabling the growing IoT revolution. One of the most common requirements that I hear about IoT electronics is that the power needs to be well understood and controlled during the design exploration… Read More

Electronic Design Automation

Virtual Emulation Extends Debugging Over Physical

Amid burgeoning complexity of SoC verification with ever increasing hardware, software and firmware content, verification engineers are hard pressed with learning multiple tools, technologies and methodologies and still completing SoC verification with full accuracy in time. The complexity, size and diversity of SoC … Read More

Will 3DIC Ever Be Cheap Enough for High Volume Products?

More news from the 3DASIP conference. Chet Palesko of SavanSys Solution had an interesting presentation with the same title as this blog (although this blog draws from several other presentations too). Chet took a look at what aspects of 3D are likely to get cheaper going forward. He took as a starting point that stuff that is not … Read More

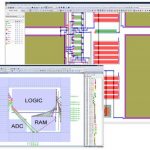

Benefits of Using Schematic Driven Layout

Most IC designs are developed by a team of professionals, often separated into distinct groups like front-end and back-end, logical and physical designers. Circuit designers use tools like schematic capture at the transistor-level to create a topology, then begin simulating the netlist with a SPICE simulator. Layout designers… Read More

A Functional Verification Framework Spanning Simulation to Emulation

Software engineers and firmware designers can find bugs, update their code and re-distribute to the users. In the consumer electronics world this means that my smart phone apps get updated, and my Android OS gets updated on a somewhat regular basis, however on the hardware side the design and verification of an SoC must be close … Read More

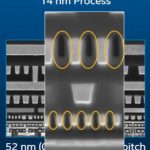

Intel has Another First for 14nm Production!

An interesting thing happened while I was researching a slide from Bill Holt’s “Advancing Moore’s Law” presentation at last month’s analyst meeting. Slide #19 mentioned that Intel was the first to use “air gap” dielectric spaces to improve performance in a digital logic flow for microprocessors. I know a certain foundry that … Read More

CTO Interview with Dr. Wim Schoenmaker of Magwel

I visited the Magwel booth at DAC in June and chatted with Dundar Dumlugol the CEO about their EDA tools that enable 3D co-simulation and extraction. Since then I’ve made contact with their CTO, Dr. Wim Schoenmaker to better understand what it’s like to start up and run an EDA company. Magwel’s history goes back… Read More

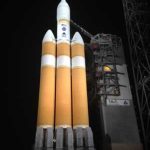

Synthesizing rad-tolerant RTL for FPGAs

The maiden voyage of NASA’s Orion spacecraft brought a raft of articles about how the flight computer inside is “no smarter than your phone,” running on wheezing IBM PowerPC 750FX processors. NASA’s deputy manager for Orion avionics, Matt Lemke, admits the configuration is already obsolete – at least in commercial terms. … Read More

Synopsys Q4 Earnings

Synopsys announced their earnings a couple of days ago. This is actually also the end of their fiscal year. They had quarterly earnings of $539M meaning that they did just over $2B for the year. Their guidance for fiscal 2015 is revenue between $2.185B to $2.225B. They said that about 80% of that revenue is already in backlog.

But it… Read More

Variation at IEDM

IEDM (technically the International Electron Devices Meeting although I’ve never heard anyone use the full name) is in a couple of weeks time, in San Francisco. It is December 15-17th at the Hilton Union Square (which is not actually at Union Square but nearby at 333 O’Farrell Street).

For the last few years on the Tuesday… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior