You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4440

[filter] => raw

[cat_ID] => 157

[category_count] => 4440

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

For a design engineer engulfed in the daily rigorous routine of having to keep in sync with updates from various design team members as well the dictums of the design management team, the task of remaining up-to-date with the design information is very often daunting.

What design changes have been checked in this week? Is the verification… Read More

With High-Level Synthesis (HLS) the first benefit that comes to my mind is reduced design time, because coding with C or SystemC is more efficient than low-level RTL code. What I’ve just learned is that there’s another benefit, a reduction in the amount of functional simulation required. One HLS customer was able … Read More

Chip design is largely about assembling pre-designed IP, either developed in other groups in the same company, or brought in from a 3rd party, or occasionally developed within the SoC design group itself. But that makes it sound like it is a bunch of blocks linked together with some interconnect, but of course another important … Read More

China Mobile’s bid to go for 3-mode Long-Term Evolution (LTE) has led to the first major breakthrough, $65 LTE handsets, and here baseband and application processors provided by chipmakers like Leadcore Technology, MediaTek and Spreadtrum Communications have all one thing in common: DSP cores from CEVA Inc.

The advent… Read More

ESD stands for electro-static discharge and deals with the fact that chips have to survive in an electrically hostile environment: people, testers, assembly equipment, shipping tubes. All of these can carry electric charge that has the “potential” (ho-ho) to damage the chip irreversibly. Historically this was… Read More

I remember a couple of decades ago, my father used to go to a nearby doctor’s clinic to get his blood pressure and sugar levels checked. I guess, in around 1990s small electronic kits became available to measure these usual daily health indicators and instantly display the numbers. I bought a few for my father then. Today, the scene… Read More

Engineers love acronyms and my latest blog post has three acronyms in the title alone, so hopefully you are doing or considering SoC designs with the AMBA AXI4(Advanced eXtensible Interface 4) interface specification along with PCI Express (Peripheral Component Interconnect Express). One big motivation for using semiconductor… Read More

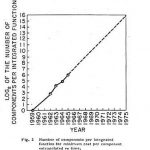

Earlier this week it was the Synopsys user group meeting SNUG. Not just any old SNUG but the 25th Annual SNUG. The first one was 15th March 1991 and was attended by 100 people. At the time, Synopsys had annual revenues of $22M. This year, the various SNUGs around the world will have a total attendance of 10,000 people and Synopsys revenue… Read More

Today an SoC cannot be without multiple IP blocks integrated together in the most optimal manner. In such an environment, it’s natural that interoperability and configurability of an IP get prime considerations to achieve the best PPA (Power, Performance and Area) for the SoC containing that IP. While PPA is a basic criterion … Read More

After teams sweat the details of SoC and industrial design, they turn to printed circuit board designers for magic. Here are a pile of chips and passives, and a schematic for interconnecting them. This is how much physical space the board can occupy. Connectors have to be here, and here, and mounting holes there, and there. There … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era