It appears so. Why there is so much rush towards FD-SOI in recent days? Before talking about the game, let me reflect a bit on the FD-SOI technology first. The FD-SOI at 28nm claims to be the most power-efficient and lesser cost technology compared to any other technology available at that node. There are many other advantages from… Read More

Electronic Design Automation

The Best Conversations You Missed at #52DAC!

The CEO Fireside Chats were my very favorite part of #52DAC. Dr. Walden Rhines, Lip-Bu Tan, and Dr. Aart de Geus are heroes of the EDA industry, absolutely. I saw all three Fireside Chats and the one word that I’m left with is INSPIRED! … Read More

DDR stands for Don’t Do (Just) RTL

In optimizing SoC design for performance, there is so much focus on how fast a CPU core is, or a GPU core, or peripherals, or even the efficiency of the chip-level interconnect. Most designers also understand selecting high performance memory at a cost sweet spot, and optimizing physical layout to clock it as fast as possible within… Read More

New Tool Suite to Accelerate SoC Integration

Today, an SoC is seen in the context of an optimized assembly of IPs; it’s no more a single monolithic chip design. It’s very common to see an ARM processor IP along with an interconnect IP, a memory IP, and couple of buses and interfaces IP in an SoC. Although the SoC seems to be an integrated collection of IPs, it can be very complex and… Read More

High Level Synthesis. Are We There Yet?

High level synthesis (HLS) seems to have been part of the backdrop of design automation for so long that it seems to be one of those things that nobody notices any more. But it has also crept up on people and gone from interesting technology to keep an eye on to getting genuine adoption. The first commercial product in the space was behavioral… Read More

I Don’t Know Much About Aart…

Actually, like anyone who has been in EDA for more than a decade or two (or three) I know quite a bit about Aart. But I still learned quite a bit about his views at the Fireside Chat at DAC where Ed Sperling talked to Aart for three-quarters of an hour.

Aart has a great talent at taking various small trends in the industry and aggregating … Read More

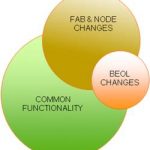

Design Data Management: An Analog IP Porting Case Study

IQ-Analog Corp. offers “off-the-shelf” data converter intellectual property (IP) for multiple foundries. The San Diego, California–based semiconductor design firm also provides analog front-end (AFE) technology that it tailors according to customer needs. And that’s where the dilemma begins.

IQ-Analog’s… Read More

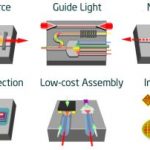

Why silicon photonics and 2.5D design go together

Silicon photonics is one of the upstart “More than Moore” technologies designed to enable the next generation of high-performance devices. Photonic design is the art of moving and transforming signals in the form of photons, allowing the message to literally travel at the speed of light, and bringing the promise of significant… Read More

Predictions about EDA and IP at #52DAC

On Sunday night at DAC this week I sat in the front row and listened to Gary Smith give his predictions about EDA and IP as an industry. His financial forecast was a $6.8B industry in 2015, growing to $9B in 2019. An ideal company for Wall Street to invest in would have slow and steady growth. If you add semiconductor IP into the forecast… Read More

EDA Acquisition to Drive SoC realization

A week ago I was reading an article written by Daniel Nenni where he emphasised about semiconductor acquisitions to fuel innovation. We would see that in a larger space, not only in semiconductor and FPGA manufacturing companies (e.g. Intel and Altera) but also in the whole semiconductor ecosystem. If we see it from technical perspective,… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era