The NFL has its annual Super Bowl contest each year, EDA vendors attend DAC, then the test folks attend ITCwhich was in Anaheim a few weeks ago. I’ve marketed ATGP, BIST and DFT tools before so I like to keep updated on what’s happening at conferences like ITC. Robert Ruiz from Synopsys spoke with me by phone to provide … Read More

Electronic Design Automation

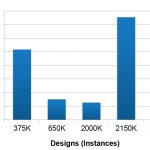

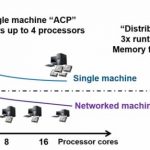

Why FPGA synthesis with Synplify is now faster

The headline of the latest Synopsys press release drops quite a tease: the newest release of Synplify delivers up to 3x faster runtime performance in FPGA synthesis. In our briefing for this post, we uncovered the surprising reason why – and it’s not found in their press release.… Read More

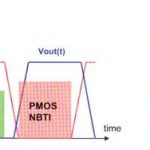

FinFET Reliability Analysis with Device Self-Heating

At the recent TSMC OIP symposium, a collaborative presentation by Synopsys and Xilinx highlighted the importance of incorporating the local FinFET device self-heating temperature increase on the acceleration of device reliability mechanisms.… Read More

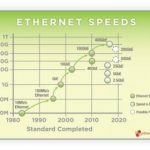

How Virtualization Makes Network Processor Verification Efficient

When Ethernet was introduced in 1983 it ran at 10Mbps and mostly relied on hubs and coaxial cable. Twelve years later a faster speed was introduced, running at 100Mbps. Since then we have seen an acceleration of new data rate introductions. According top the Ethernet Alliance, Ethernet could have 12 speeds before 2020, with 6 of … Read More

Interconnect Watch: 3 Chip Design Merits for Network Applications

The countdown to the end of Moore’s Law is coinciding with the rising complexity in system-on-chip (SoC) designs. And that’s not a mere coincidence. The leverage that has long been coming from shrinking process nodes in terms of cost, performance and power benefits is now increasingly being accomplished through… Read More

Price of Admission $0.00 at Inaugural Silicon Valley Conference

Back in 2002, the Southwest DFT Conference was born and experts on design for test (DFT) and test got together to share ideas and talk to people in this industry that were trying to solve test challenges of the day.… Read More

About That Landauer Limit…

You may have heard of the Landauer principle or the Landauer limit. This defines a lower bound on switching power dissipation in any form of digital circuit. Rolf Landauer first presented this principle in 1961, while working at IBM. It’s not limited by how the circuit is built – you can use FinFETS or spintronics or even dilithium… Read More

IoT chipsets and enterprise emulation tools

When most people talk about the IoT, it is usually all about wearables-this and low-power-that – because everyone is chasing the next huge consumer post-mobile device market. Mobile devices have provided the model. The smartphone is the on-ramp to the IoT for most consumers, with Bluetooth, Wi-Fi, and LTE, and maybe a dozen or … Read More

Learning about 3D Integration of ICs and Systems

We blog a lot about Moore’s Law, and even “More than Moore” where 3D integration of ICs and systems are used to get lower product costs. One big challenge with 3D integration of ICs is that most EDA software was really intended only for abstracting at 2D or 2.5D structures. Over the past several years there have … Read More

Our Own Cadence Amongst the Best Multinational Workplaces!

There were some very happy faces around MemCon this week for a variety of reasons. Paul McLellan was smiling because he now works full time for Cadence and has the best medical benefits ever and of course I was smiling because there was free food! … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center