Leading edge SoC designs can contain billions of transistors, cost over $10M to design, and take over 18 months to deliver, but not all SoCs require that much complexity, cost and time. In fact, there is a growing class of SoC designs that integrate the popular ARM Cortex-M0 processor along with analog blocks that work with sensors… Read More

Electronic Design Automation

Samsung Should Just Buy eSilicon Already!

As you all know I’m a big fan of the ASIC business dating back to the start of the fabless semiconductor transformation where anybody could send a design spec to an ASIC company and get a chip back. The ASIC business model also started the smart phone revolution when Samsung built the first Apple SoCs for the iPhones and iPads.

Today … Read More

SRAM Optimization Saves Power on SOC’s and in Systems

Mobile device designers face the dilemma of reducing power and at the same time maintaining or increasing performance. Consumers will not tolerate increased battery life at the expense of performance. If it were otherwise, designers could simply dial back clock rates. Without this simple cure, the best way to reduce power for… Read More

Joe Costello and Other Luminaries Keynote at DAC

The most charismatic EDA CEO that I have ever witnessed is Joe Costello, who formed Cadence by merging SDA (Solomon Design Automation) and ECAD (known for DRC with Dracula). You will be impressed with his Monday keynote at DACon June 19th, starting at 9:15AM. Joe has long since left the EDA world and is currently the CEO of a company… Read More

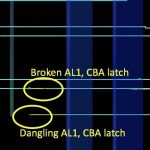

Recipes for Low Power Verification

Synopsys hosted a tutorial on verification for low power design at DVCon this year, including speakers from Samsung, Broadcom, Intel and Synopsys. Verification for low power is a complex and many-faceted topic so this was a very useful update. There is a vast abundance of information in the slides which I can’t hope to summarize… Read More

Aldec Swings for the Fences

In today’s fast-moving technology markets, companies who are prepared to step up to opportunity can break out of traditional bounds to become players in bigger and fast-growing markets. It looks to me like Aldec is putting itself on that path. They have announced an end-to-end hardware/software co-verification solution… Read More

Six Reasons to Consider Using FPGA Prototyping for ASIC Designs

There’s no doubt that programmable logic in FPGAs have transformed our electronics industry for the better. If you do ASIC designs then there’s always the pressure of getting first silicon correct, with no functional or timing bugs, because bugs will cause expensive re-spins and delay time to market. ASIC designers… Read More

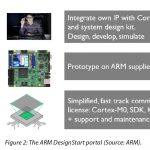

Securing Your IoT System using ARM

I’ll never forget reading about and experiencing the October 21, 2016 Distributed Denial of Service (DDoS) attacks which slowed and shut down a lot of the Internet. On that particular attack the target was to shut down the Domain Name System (DNS). Traffic for this massive DDoS attack came from IoT devices which were unsecured… Read More

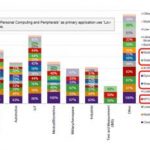

Unlocking Access to SOC’s for IoT Edge Product Developers

In the wake of the many mega mergers and consolidation in the semiconductor and electronics space, it is easy to say that opportunities for smaller companies are shrinking. Indeed, quite the opposite might be true. The larger companies, like Broadcom, ARM, Qualcomm, Analog Devices, Microchip, Maxim and Infineon (to name a few)… Read More

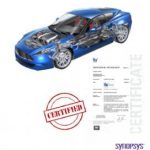

Driver Assistance and Autonomous? Need ASIL D Ready Certified CPU!

The automotive segment is moving from a kind of niche, filled with commodities and highly specialized low complexity IC, to an innovative and very dynamic segment attracting most of the big players, from Qualcomm to Nvidia or Intel. These chip makers are targeting automotive as they need to find new growth areas, and they have quickly… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center