The bleeding edge of SoC design was on full display last month at DAC in Austin as I listened to a panel session where members talked about their specific experiences so far designing with the 7nm process node. Jim Hogan was the moderator and the panel quickly got into what their respective companies are doing with 7nm technology already.… Read More

Electronic Design Automation

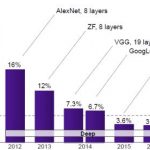

Synopsys New EV6x Offers 4X More Performance to CNN

When Synopsys bought Virage Logic in 2010, ARC processor IP was in the basket, but at that time ARC processor core was not the most powerful on the market, and by far. The launch of EV6x vision processor sounds like Synopsys has moved ARC processor core by several orders of magnitude in term of processing power. EV6x deliver up to 4X … Read More

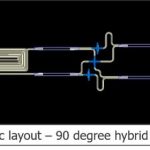

Mentor & Phoenix Software Shed Light on Integrated Photonics Design Rule Checking

Just prior to the opening of the 54[SUP]th[/SUP] Design Automation Conference, Mentor, a Siemens company, and PhoeniX Software issued a press release announcing a new integration between their tools to help designers of photonic ICs (PICs) to close the loop for manufacturing sign-off verification. This is a significant piece… Read More

Cadence Explores Smarter Verification

Verification as an effectively unbounded problem will always stir debate on ways to improve. A natural response is to put heavy emphasis on making existing methods faster and more seamless. That’s certainly part of continuous improvement but sometimes we also need to step back and ask the bigger questions – what is sufficient … Read More

LETI Days 2017: FD-SOI, Sensors and Power to Sustain Auto and IoT

I have attended last week to the LETI Days in Grenoble, lasting two days to mark the 50[SUP]th[/SUP] anniversary of the CEA subsidiary. Attending to the LETI Days is always a rich experience: LETI is a research center counting about 3000 research engineers, but LETI is also a start-up nursery. The presentations are ranging from … Read More

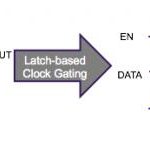

Webinar: Synopsys on Clock Gating Verification with VC Formal

Clock gating is arguably the mostly widely-used design method to reduce power since it is broadly applicable even when more sophisticated methods like power islands are ruled out. But this style can be fraught with hazards even for careful designers. When you start with a proven-correct logic design and add clock gating, the logic… Read More

ADAS and Vision from Cadence

A huge theme at #54DAC this year was all things automotive and in particular the phrase ADAS (Assisted Driver Assistance Systems), so I followed up with Raja Tabet a corporate VP of emerging technology at Cadence. We met on Monday in a press room where I quickly learned that Cadence has been serving the automotive industry for the … Read More

HW and SW Co-verification for Xilinx Zynq SoC FPGAs

It constantly amazes me at how much FGPA companies like Xilinx have done to bring ARM-based CPUs into a programmable SoC along with FPGA glue logic. Xilinx offers the Zynq 7000 and Zynq UltraScale+ SoCs to systems designers as a way to quickly get their ideas into the marketplace. A side effect of all this programability and flexibility… Read More

Capture the Light with Integrated Photonics

I wrote up a quick article in the weeks before the Design Automation Conference (DAC) letting readers know that Integrated Photonics were indeed coming to DAC again this year. As a follow up, I attended the DAC presentation, ‘Capture the Light. An Integrated Photonics Design Solution from Cadence, Lumerical and PhoeniX Software’,… Read More

Overcoming the Challenges of Creating Custom SoCs for IoT

As the Internet of Things (IoT) opportunities continues to expand, companies are working hard to bring System-on-Chip (SoC) solutions to market in the hopes of garnering market share and revenue. However, it’s not as easy as it may first seem. Companies are running into a series of issues that stand between them and capturing the… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center