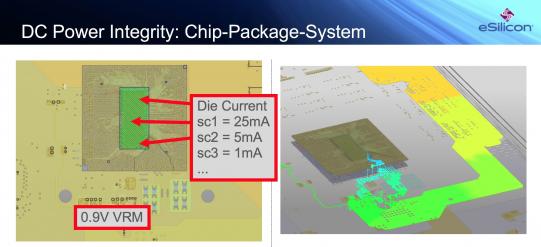

While I missed ANSYS (and indeed everyone else) at DAC this year, I was able to attend the ANSYS Innovation Conference last week at the Santa Clara Convention Center. My primary purpose for being there was to listen to a talk by eSilicon which I’ll get to shortly, but before that I sat through a very interesting presentation on the growing… Read More

Electronic Design Automation

Enabling Complex System Design Environment

Deterministic, yet versatile. Robust and integrated, yet user-friendly and easily customizable. Those are some desirable characteristics of an EDA solution as the boundaries of our design optimization, verification and analysis keep shifting. A left shift driven by a time-to-market schedule compression, while the process… Read More

Meeting Analog Reliability Challenges Across the Product Life Cycle

Create a panel discussion about analog IC design and reliability and my curiosity is instantly piqued, so I attended a luncheon discussion at #55DAC moderated by Steven Lewis of Cadence. The panelists were quite deep in their specialized fields:… Read More

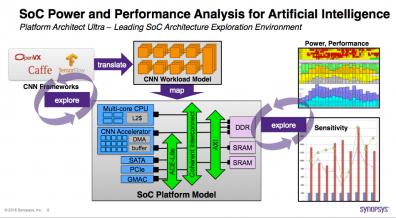

Architecting an ML Design

Discussion on machine learning (ML) and hardware design has been picking up significantly in two fascinating areas: how ML can advance hardware design methods and how hardware design methods can advance building ML systems. Here I’ll talk about the latter, particularly about architecting ML-enabled SoCs. This approach is … Read More

A True Signoff for 7nm and Beyond

The Tale of Three Metrics

Meeting PPA (Performance, Power and Area) target is key to a successful design tapeout. These mainstream QoR (Quality of Results) metrics are rather empirical yet inter-correlated and have been expanded to be linked with other metrics such as yield, cost and reliability. While the recent CPU performance… Read More

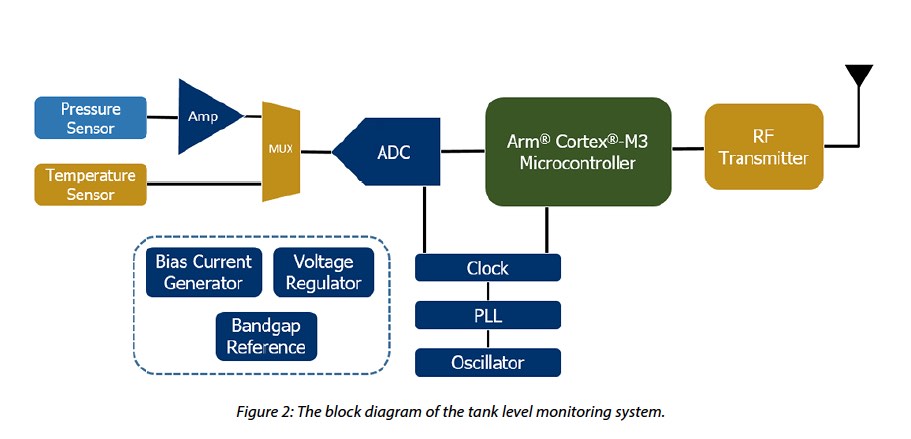

Living on the (IoT) Edge

The phrase “where the rubber meets the road” is especially apt when it comes to discussions about the Internet of Things. The obvious interpretation is that dissimilar things are being put together in a mutually dependent fashion. When I hear the phrase I always think of the things that can go wrong, such a tire sliding instead of … Read More

Enhancing Early Static FSM

Finite state machines (FSMs) are widely adopted as part of reactive systems to capture their dynamic behaviors using a limited number of modes or states that usually change according to the applied circumstances. Some terminologies are frequently used to describe the FSM characteristics: state, transition, condition and … Read More

Cadence Update on AMS Design and Verification at #55DAC

As a blogger in the EDA industry I get more invitations to meet with folks at DAC than I have time slots, so I have to be a bit selective in who I meet. When the folks at Cadence asked me to sit down and chat with Mladen Nizic I was intrigued because Mladen is so well-known in the AMS language area and he’s one of the authors of, The Mixed-Signal… Read More

Synopsys Offers First Single-Vendor Comprehensive Photonic IC Design Flow

Synopsys has a long history of being a thought leader and it’s not surprising to see the company jumping into the forefront of new technologies. For decades, I’ve been steeped in electronic IC design and it caught me by surprise to find that Synopsys had been quietly working on filling out their portfolio in the optical design solutions… Read More

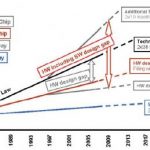

An update on the Design Productivity Gap

Over a decade ago, a group of semiconductor industry experts published a landmark paper as part of the periodic updates to the International Technology Roadmap for Semiconductors, or ITRS for short (link). The ITRS identified a critical design productivity gap. The circuit capacity afforded by the Moore’s Law pace of technology… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center