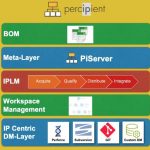

Earlier this month I attended a webinar organized by Methodics on the topic of IP life cycle management and traceability, with three presenters and a Q&A session at the end. I’ve worked with Michael Munsey before and he was the first presenter. Semiconductor IP creation and re-use is the foundation of all modern IC designs,… Read More

Electronic Design Automation

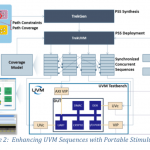

Breker on PSS and UVM

When PSS comes up, a lot of mainstream verification engineers are apt to get nervous. They worry that just as they’re starting to get the hang of UVM, the ivory tower types are changing the rules of dynamic verification again and that they’ll have to reboot all that hard-won UVM learning to a new language. The PSS community and tool … Read More

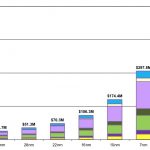

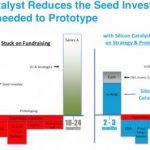

Learning on the Edge Investment Thesis

It is said that it will cost as much as $600M to develop a 5nm chip. At that price, only a few companies can afford to play, and with that amount of cash in, innovation is severely limited.

At the same time, there is a stampede in the artificial intelligence (AI) market where around 60 startups have appeared, many of which have already … Read More

IC to Systems Era

One of my favorite EDA disruptions is the Siemens acquisition of Mentor, pure genius. Joe Sawicki now runs the Mentor IC EDA business for Siemens so we will be seeing him at more conferences and events than ever before. Joe did a very nice keynote at the recent U2U conference that I would like to talk about before we head to the 56thDAC… Read More

The IoT will meet 5G soon, but not with the old SIM cards

By now you have probably realized that 5G is a lot more than an incremental change from previous 3G and 4G cellular technology. For instance, 5G will be used to connect our phones in completely new ways, such as with microcells in urban areas using mm-wavelength signals. 5G will also include two low power protocols that are intended… Read More

56thDAC ClioSoft Excitement

As the number one 56thDAC supporting portal we will publish what’s happening in the conference, on the exhibit floor, and outside activities. The SemiWiki bloggers will be out in full force with live coverage and behind the scenes looks. Remember, SemiWiki bloggers are actual semiconductor professionals with hundreds… Read More

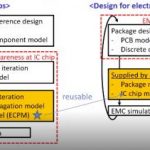

Getting to EMC Compliance by Design

At the risk of highlighting my abundant lack of expertise in the domain, I had always viewed EMC (electromagnetic compatibility) compliance and testing as one of those back-end exercises that can only be done on the real device and depends on a combination of expertise and brute-force in chip/package/module/system design (decaps,… Read More

Achieving a Predictable SignOff in 7nm

Designing with advanced-nodes FinFETs such as 7nm node involves a more complex process than prior nodes. As secondary physical effects are no longer negligible, the traditional margin-based approach applied at various design abstraction levels is considered ineffective. Coupled with the increase of device counts, failing… Read More

Re Energizing Silicon Innovation

Hardware is roaring back into prominence in technology innovation, from advanced cars to robots, smart homes and smart cities, 5G communication and the burgeoning electronification of industry, medicine and utilities. While software continues to play a role, all of these capabilities depend fundamentally on advances in … Read More

Anirudh Keynote at CDNLive 2019

Anirudh Devgan (President of Cadence), gave the third keynote at CDNLive Silicon Valley this year. He has clearly become adept in this role. He has a big, but supportable vision for Cadence across markets and technologies and he’s become a master of the annual tech reveals that I usually associate with keynotes.

Anirudh opened … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era