At the ES Design West event in San Francisco last week Silvaco’s CTO and EVP of Products, Babak Taheri, gave a presentation titled, “Next Generation SoC Design: From Atoms to Systems”. The time slot for the talk was only 30-minutes which is simply not enough to discuss all the technology Silvaco is providing now. I had not looked closely… Read More

Electronic Design Automation

WEBINAR: Eliminating Hybrid Verification Barriers Through Test Suite Synthesis

I’ve been following the evolution of the verification space for a very long time including several stints consulting to formal verification companies. It has always been interesting to me to see how so many diverse verification techniques emerge and been used, but without much unification of the approaches. With the emergence… Read More

HBM or CDM ESD Verification – You Need Both

In the realm of ESD protection, Charged Device Model (CDM) is becoming the biggest challenge. Of course, Human Body Model (HBM) is still essential, and needs to be used when verifying chips. However, a number of factors are raising the potential losses that CDM events can cause relative to HBM. These factors fall into two categories:… Read More

Konica Minolta Talks About High-Level Synthesis using C++

In the early days of chip design circa 1970’s the engineers would write logic equations, then manually reduce that logic using Karnaugh Maps. Next, we had the first generation of logic synthesis in the early 1980’s, which read in a gate-level netlist, performed logic reduction, then output a smaller gate-level netlist.… Read More

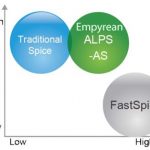

WEBINAR: GPU-Powered SPICE – The Way Forward for Analog Simulation

Several years ago, I was a consultant to a company called Gauda, Inc. I enjoyed working with Gauda as the technology was interesting. On June 3, 2014, Gauda, Inc. was acquired by D2S, Inc. so their technology lives on. Gauda was focused on optical proximity correction (OPC) and optical proximity verification solutions utilizing… Read More

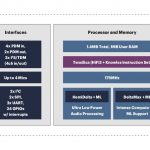

Smart Hearing is Heating Up

A lot of the attention in intelligent systems is on object detection in still or video images but there’s another very active area, in smart audio. Amazon and Google smart speakers may be the best-known applications but there are more obvious (and perhaps less novelty-driven) applications in enhancing the hearing devices we already… Read More

Automotive Market Pushing Test Tool Capabilities

It’s easy to imagine that the main impetus for automotive electronics safety standards like ISO 26262 is the emergence of autonomous driving technology. However, even cars that do not offer this capability rely heavily on electronics for many critical systems. These include engine control, braking, crash sensors, and stability… Read More

Early IP Block Error Detection is Critical!

The rising complexity of modern SoC designs, as enabled by progressing manufacturing technology, leads to an increasing validation challenge as the only way to manage complexity increase is by re-using more pre-designed IP blocks. These IP-blocks are provided by various suppliers such as a foundry partner, internal design… Read More

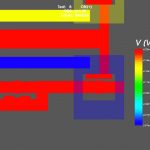

#56DAC Update – What’s New at Concept Engineering

I first connected with Gerhard Angst of Concept Engineering over 15 years ago, because I was using their SpiceVision PRO tool to visual SPICE netlists received from customer designs to be debugged in a FastSPICE circuit simulator. The ability to visualize a transistor-level netlist was simply essential to quickly understanding… Read More

An Important Next Step for Portable Stimulus Adoption

Portable stimulus has been a hot topic for a couple of years in the EDA and semiconductor industries. Many observers see this approach as the next major advance in verification beyond the Universal Verification Methodology (UVM), and the next step higher in abstraction for specifying verification intent. The basic idea is to … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era