With many design teams still searching for an effective means of identifying Charged Device Model (CDM) issues early in the design process, it comes as no surprise that events on this topic generate a lot of interest and are well attended. In July Magwel’s CEO Dr. Dundar Dumlugol had the honor of being invited by Professor Ming-Dou… Read More

Electronic Design Automation

Cadence Celsius Heats Up 3D System-Level Electro-Thermal Modeling Market

A few years back people were saying that the “EDA” problem was solved and that design tools had become commodity. At the same time people hailed ADAS, smart homes, mobile communication and AI as the frontiers of electronics. Perhaps it could be said that layout tools, routers, placers, and circuit simulators had largely matured… Read More

Speeding Up Physical Failure Analysis (PFA)

The cost of an IC depends on many factors like: NRE, masks, fabrication, testing, packaging. Product engineers are tasked with testing each part and understanding what exactly is limiting the yields. Every company has a methodology for Physical Failure Analysis (PFA), and the challenge is to make this process as quick as possible,… Read More

WEBINAR: AI-Powered Automated Timing Arc Prediction for AMS IP’s

A directed approach to reduce Risk and improve Quality

Safety and reliability are critical for most applications of integrated circuits (ICs) today. Even more so when they serve markets like ADAS, autonomous driving, healthcare and aeronautics where they are paramount. Safety and reliability transcend all levels of an integrated… Read More

Automatic Documentation Generation for RTL Design and Verification

Ask any hardware or software engineer working on a product, and they will tell you that writing documentation is a pain. Customers have high expectations for user manuals and reference guides, usually requiring a team of technical writers to satisfy their requirements. In order to meet time-to-market deadlines, documentation… Read More

WEBINAR: Reusing Your IPs & PDKs Successfully With Cadence® Virtuoso®

I recently wrote about a ClioSoft® study with Google on using cloud platforms for EDA design and the importance of using persistent storage when doing that. ClioSoft will again be sharing important information on design productivity in the upcoming webinar, Reusing Your IPs & PDKs Successfully With Cadence® Virtuoso®. … Read More

Chapter Ten – Design Automation for Systems

Electronic design automation has evolved to an extent that the complex chips with tens of billions of transistors frequently produce first pass functional prototypes from the manufacturer. What makes this so incredible is that such a small portion of the possible states of electronic operation are actually tested in the simulation… Read More

Synopsys is First IP Provider with a Complete CXL Implementation Available

Synopsys just announced the availability of their IP solution supporting CXL (Compute Express Link). This new protocol is going to be an important component for several applications expected to be shipping starting in 2021. CXL is an alternate protocol that runs on the same physical layer as PCI Express (PCIe). Among other usages,… Read More

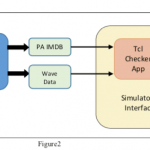

Tcling Your Way to Low Power Verification

OK – maybe that sounds a little weird, but it’s not a bad description of what Mentor suggests in a recent white-paper. There are at least three aspects to power verification – static verification of the UPF and the UPF against the RTL, formal verification of state transition logic, and dynamic verification of at least some critical… Read More

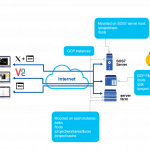

For EDA Users: The Cloud Should Not Be Just a Compute Farm

When EDA users first started considering using cloud services from Google, Amazon, Microsoft, and others, their initial focus was getting access for specific design functions, such as long logic or circuit simulation runs or long DRC runs, not necessarily for their entire design flow. If you choose to use the cloud this way, you… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era