Sidenserecently conducted a webinar on what they call the Smart Connected Universe. They consider the Smart Connected Universe as something that includes a collection of market segments that are both smart and connected. This casts a big net, and includes what many are calling IoT, but goes further into medical, automotive and… Read More

Author: Tom Simon

Calibre xACT Shakes Up 16nm and Below Extraction Game

Mentor Graphics made a big announcement regarding SOC extraction at their User2User conference in San Jose during April. Before I get to the meat of the announcement, I’d like to reflect back on the early days of Calibre-DRC at Mentor. I was in Sales at Mentor around 1999, and Calibre-DRC was the new kid on the block. We had to go convince… Read More

TSV Modeling Key for Next Generation SOC Module Performance

The use of silicon interposers is growing. Several years ago Xilinx broke new ground by employing interposers in their Virtex®-7 H580T FPGA. Last August Samsung announced what they say is the first DDR4 module to use 3D TSV’s for enterprise servers. Their 64GB double data rate-4 modules will be used for high end computing where … Read More

Sidense NVM Scores Qualification on GLOBALFOUNDRIES 28nm SLP and HPP

A tremendous number of chips being designed for today’s products require some sort of onboard data storage. The size of these needs range from a handful of bytes, for trim and calibration storage, to something much more substantial like boot code storage. In both of these examples the storage ideally should be nonvolatile, with… Read More

ANSYS Event to Highlight Cutting Edge Technology Development

If you follow technology news, it would be hard to deny that we live in exciting times. In some ways there is an unparalleled amount of big and cool technology development going on right now. We all have followed the rise of Tesla Motors. They took over a long vacant US big-auto plant in Fremont and are reinventing the US automobile industry.… Read More

Intel and the Intel-of-Things

When I joined Calma in 1982, Intel was a small company making microprocessor chips in a crowded marketplace. They had scored big with IBM who was using their 8088 in the very first personal computer. Wind River was a hatchling with David Wilner and Jerry Fiddler working out of a rented warehouse in Berkeley – I know, I hung out… Read More

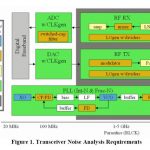

Full Spectrum Analog FastSPICE Useful for RF Designs on Bulk CMOS

It has been about a year since the acquisition of Berkeley Design Automation by Mentor Graphics. Berkeley was doing quite well in the somewhat crowded SPICE simulator market. In many respects they broke new ground for high speed and accurate SPICE simulators. Since the acquisition we know that former Berkeley executives are now… Read More

Mapping Focus and Dose onto BEOL Fabrication Effects

With today’s ArF based lithography using 193nm wavelength light, we are hard up against the limitations imposed by the Raleigh equation. Numerous clever things have been devised to maximize yield and reduce feature size. These include 2 beam lithography, multiple patterning, immersion litho processes to improve NA, thinner… Read More

Cadence’s New Implementation System Promises Better TAT and PPA

On Tuesday Cadence made a big announcement about their new physical implementation offering, Innovus, during the keynote address at the CDNLive event in Silicon Valley. Cadence CEO Lip-Bu Tan alluded to it during his kick off talk, and next up Anirudh Devgan, Senior Vice President, Digital & Signoff Group, filled in more … Read More

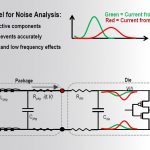

On-Chip Power Integrity Analysis Moves to the Package

Power regimes for contemporary SOC’s now include a large number of voltage domains. Rail voltages are matched closely to the performance and power requirements of various portions of the design. Indeed, some of the supply voltages are so low that the noise margins in these domains is exceedingly low. Higher voltage domains are… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era