IoT products call for a higher level of system integration than ever before. Companies seeking to go to market now have a much higher bar in terms of size, power, reliability and manufacturability. The first IoT devices evolved from embedded development boards, like the groundbreaking Arduino. These were fine for prototypes … Read More

Author: Tom Simon

Enterprise SSD SOC’s Call for a Different Interconnect Approach

The move to SSD storage for enterprise use brings with it the need for difficult to design enterprise capable SSD controller SOC’s. The benefits of SSD in hyperscale data centers are clear. SSD’s offer higher reliability due to the elimination of moving parts. They have a smaller foot print, use less power and offer much better performance.… Read More

HW Emulator Apps Open Doors to Entirely New Uses

When the topic of hardware emulation comes up, thoughts of big iron customarily come to mind. However, hardware emulation has evolved significantly and now there are other important traits that distinguish the offerings in this area. For a very long period of time emulators provided primarily a method to accelerate gate level… Read More

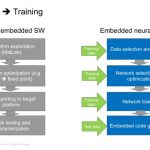

Neural Networks Ready for Embedded Platforms

If you are not yet familiar with the term Convolutional Neural Networks, or CNN for short, you are certainly bound to become in the year ahead. Using Artificial Intelligence in the form of CNN is on the verge of replacing a large number of computing tasks, especially those involving recognizing things such as sounds, shapes, objects,… Read More

A Brief History of Open-Silicon

In 2003, when Open-Silicon was founded there was a growing need for flexible and innovative ways of getting chip designs manufactured. Semiconductor companies, given the alternatives of COT or traditional ASIC, often were looking for more flexibility without the huge investment and risk of going COT. Let’s look at how Open-Silicon… Read More

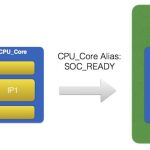

The (not so) Easy Life of an SOC Design Integrator

How can large SOC projects effectively integrate sub blocks and IP into a stable version for release or internal development? The person responsible for integrating SOC sub blocks into a validated configuration for release has a difficult task. Usually there are many sub-blocks, each undergoing their own development. There… Read More

IP Vendor Nabs Top Talent from Semiconductor Industry

The growth of mobile and IoT have helped increase the demand for One Time Programmable Non Volatile Memory (OTP NVM) as a solution for on-chip storage. To continue to meet this demand and grow with it, industry leading Sidense has recently brought on board seasoned semiconductor executive Ken Wagner as VP of Engineering. He was … Read More

FinFET will finally arrive for GPU’s in 2016

It used to be that GPU chips moved to new process nodes pretty frequently, previously as often as annually. That is up until 2011. That was the year that 28nm GPU’s were unveiled. Since then there has been a long pause. Now in the wake of the 2016 CES both Nvidia, with its previously announced Pascal, and AMD, with the just announced Polaris,… Read More

Do You Need a 3D Printer Yet?

There is no question: you will own a 3D printer – it’s only a matter of time. The situation today is like it was with the early personal computers, at first it was the hobbyists who had them and most other people wondered what they would use one for. But over time their usefulness became obvious and the difficulty of acquiring, using and… Read More

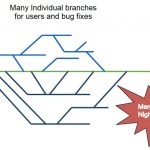

How to Overcome HW Project Release Nightmares

Is a software development release methodology a “square peg in a round hole” when it comes to hardware design? To answer this question we have to look at how exactly hardware design projects differ from their software counterparts. Intuitively we know they are fundamentally different. Let’s take a second to dig deeper to understand… Read More

Tesla and Samsung Relationship Update