In the wake of the many mega mergers and consolidation in the semiconductor and electronics space, it is easy to say that opportunities for smaller companies are shrinking. Indeed, quite the opposite might be true. The larger companies, like Broadcom, ARM, Qualcomm, Analog Devices, Microchip, Maxim and Infineon (to name a few)… Read More

Author: Tom Simon

Improved Timing Closure for Network-on-Chip based SOC’s

Network on chip (NoC) already has a long list of compelling reasons driving its use in large SOC designs. However, this week Arteris introduced their PIANO 2.0 software that provides an even more compelling reason to use their FlexNoC architecture. Let’s recap. Arteris FlexNoC gives SOC architects and designers a powerful tool… Read More

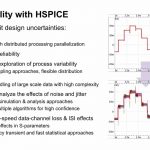

Using HSPICE StatEye to Tackle DDR4 Rail Jitter

The world is a risky place, according to Scott Wedge, Principal R&D Engineer at Synopsys, who presented at the Synopsys HSPICE SIG on Feb 2[SUP]nd[/SUP] in Santa Clara. Indeed, the world circuit designers face can be uncertain. Dealing with risk and departure from ideal was a main theme in the fascinating talks at this dinner… Read More

FPGA Design Gets Real

FPGA’s have become an important part of system design. It’s a far cry from how FPGA’s started out – as glue logic between discrete logic devices in the early days of electronic design. Modern day FPGA’s are practically SOC’s in their own right. Frequently they come with embedded processor cores, sophisticated IO cells, DSP,… Read More

On-Chip Power Distribution Networks Get Help from Magwel’s RNi

Counting squares is a useful tool for calculating simple resistance in wires, but falls short in reality when wires deviate from ideal. Frequently the use of RC extraction tools for determining resistance in signal lines in digital designs can be effective and straightforward. However, there are classes of nets in designs that… Read More

Timing Closure Complexity Mounts at FinFET Nodes

Timing closure is the perennial issue in digital IC design. While the specific problem that has needed to be solved to achieve timing closure over the decades has continuously changed, it has always been a looming problem. And the timing closure problem has gotten more severe with 16/14nm FinFET SoCs due to greater distances between… Read More

Intel Conveys Compute Card Capabilities at CES

Intel is once again adding a new computing form factor to the mix. At CES Intel announced its new Intel Compute Card. It combines CPU, GPU, DRAM, storage, WiFi, and communications inside a small modular housing slightly larger than a credit card and about 5mm thick. Intel already offers its Compute Stick, but it is limited in its interface… Read More

Qualcomm Hit With $853M Penalty for Patent Licensing Practices

Qualcomm was hit in December with a $853M fine by the Korea Fair Trade Commission (KFTC) for not fairly sharing patents related to mobile phone chipsets. In setting the standards for CDMA, WCDMA and LTE, agreements were struck that enable sharing technology to advance the standard. Fair, Reasonable and Non-Discriminatory (FRAND)… Read More

CEO Interview: Dündar Dumlugöl of Magwel

Magwel CEO Dündar Dumlugöl is well known from his days at Cadence, where I first met him, and for his more recent tenure at Magwel. At Cadence he led the team that first developed Spectre. He has come a long way from the start of his career at IMEC in Belgium. He and I had a chance to have a conversation recently where he offered insights … Read More

Building a Solar Powered Ice Freezer

My vacation is your worst nightmare. Well, at least that is what the bumper sticker says – it’s referring to Burning Man. It’s well known that among the tens of thousands of people attending this arts festival in Nevada at the end of each Summer there are lots of high tech luminaries. I also have gone many times – not to say that I am a luminary.… Read More

Breker Hosts an Energetic Panel on Spec-Driven Verification