On their first quarter earnings call Intel announced that volume production of 10nm has been moved from the second half of 2018 to 2019 due to yield issues. Specifically, they are shipping 10nm in low volume now, but yield improvement has been slower than anticipated. They report that they understand the yield issues but that improvements… Read More

Author: Scotten Jones

Intel 10nm Yield Issues

Samsung is Starting 7nm Production with EUV in June

There is a report in the Seoul Economic Daily that Samsung has completed development of their 7nm process using EUV and that production will begin in June. What is claimed in the report is:

- The process is installed in the Hwaseong S3 Fab

- Samsung has more than 10 EUV systems installed

- Production starts in June with Qualcomm, Xilinx,

Cleaning Trends for Advanced Nodes

I was invited to give a talk at the Business of Cleans Conference held by Linx Consulting in Boston on April 9th. I am not a cleans expert but rather was invited more to give an overview talk on process technology trends and the impact on cleans. In this write up I will discuss my presentation. I discussed each of the three main leading-edge… Read More

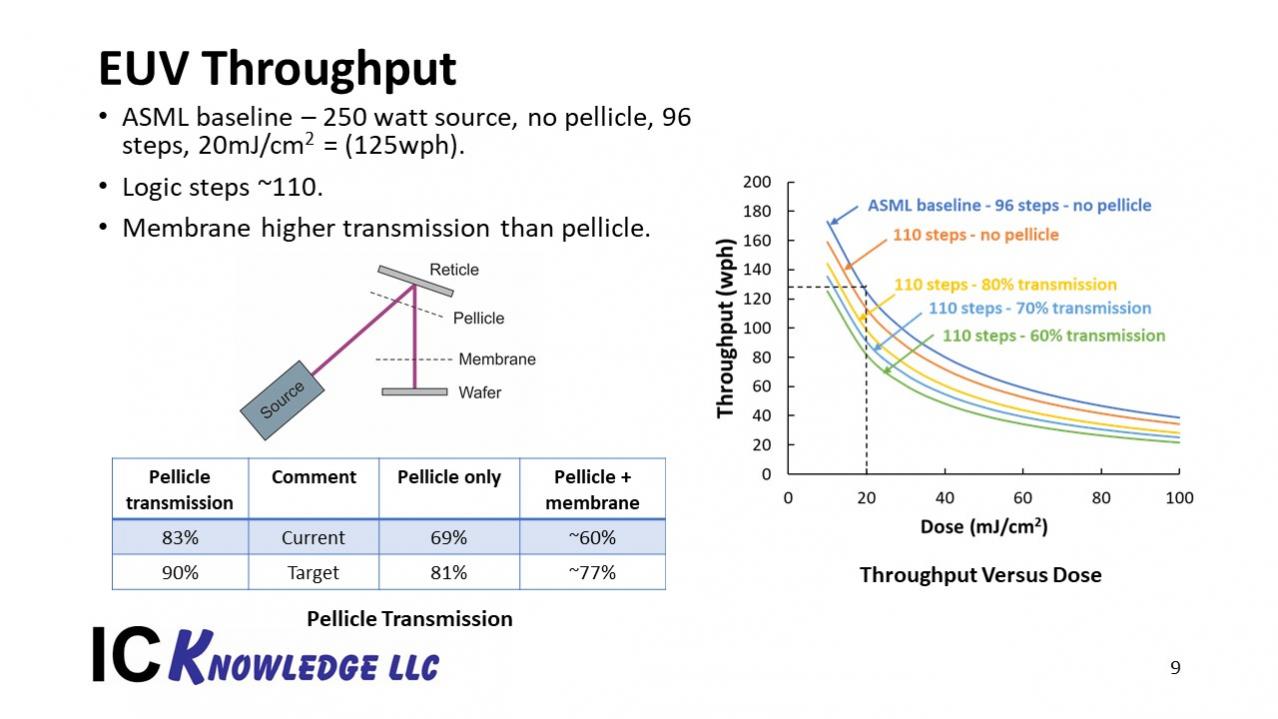

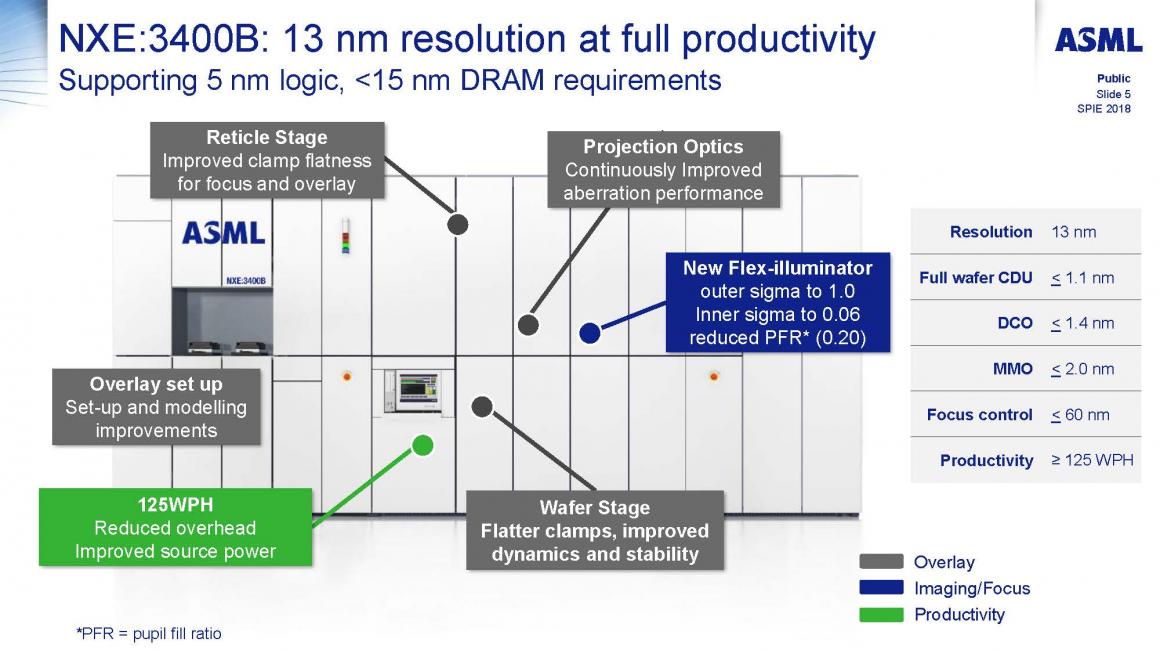

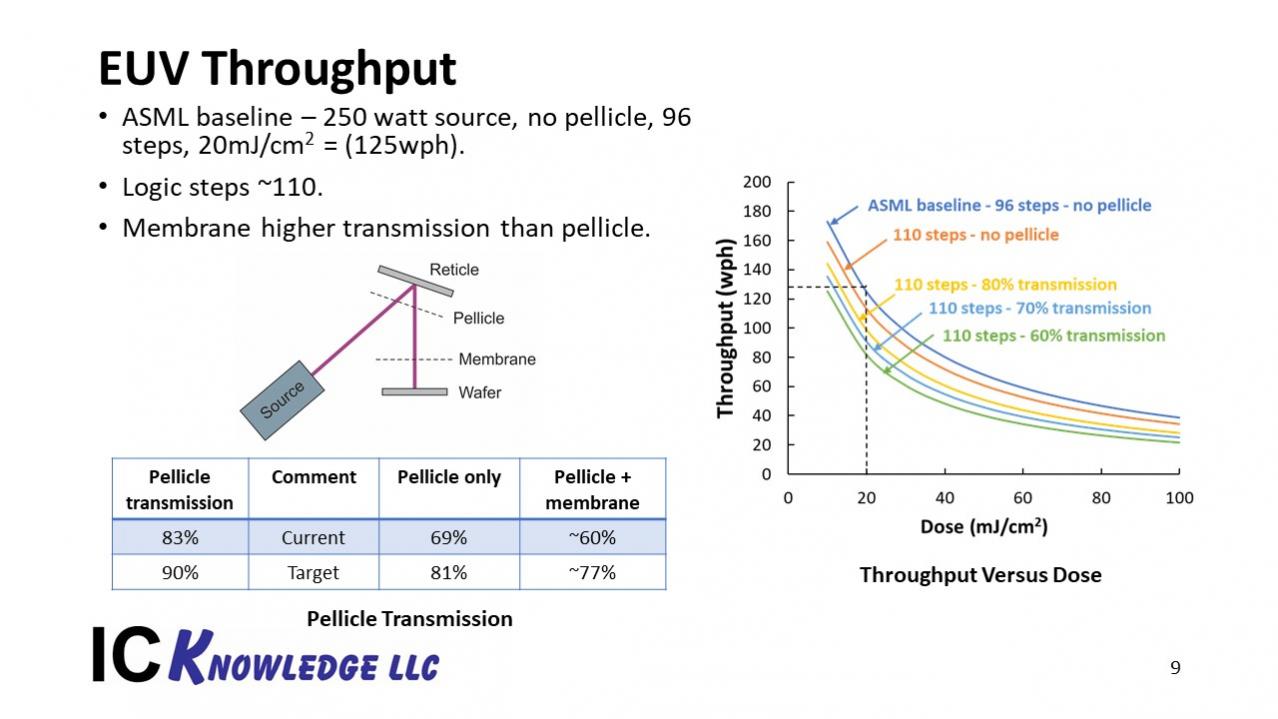

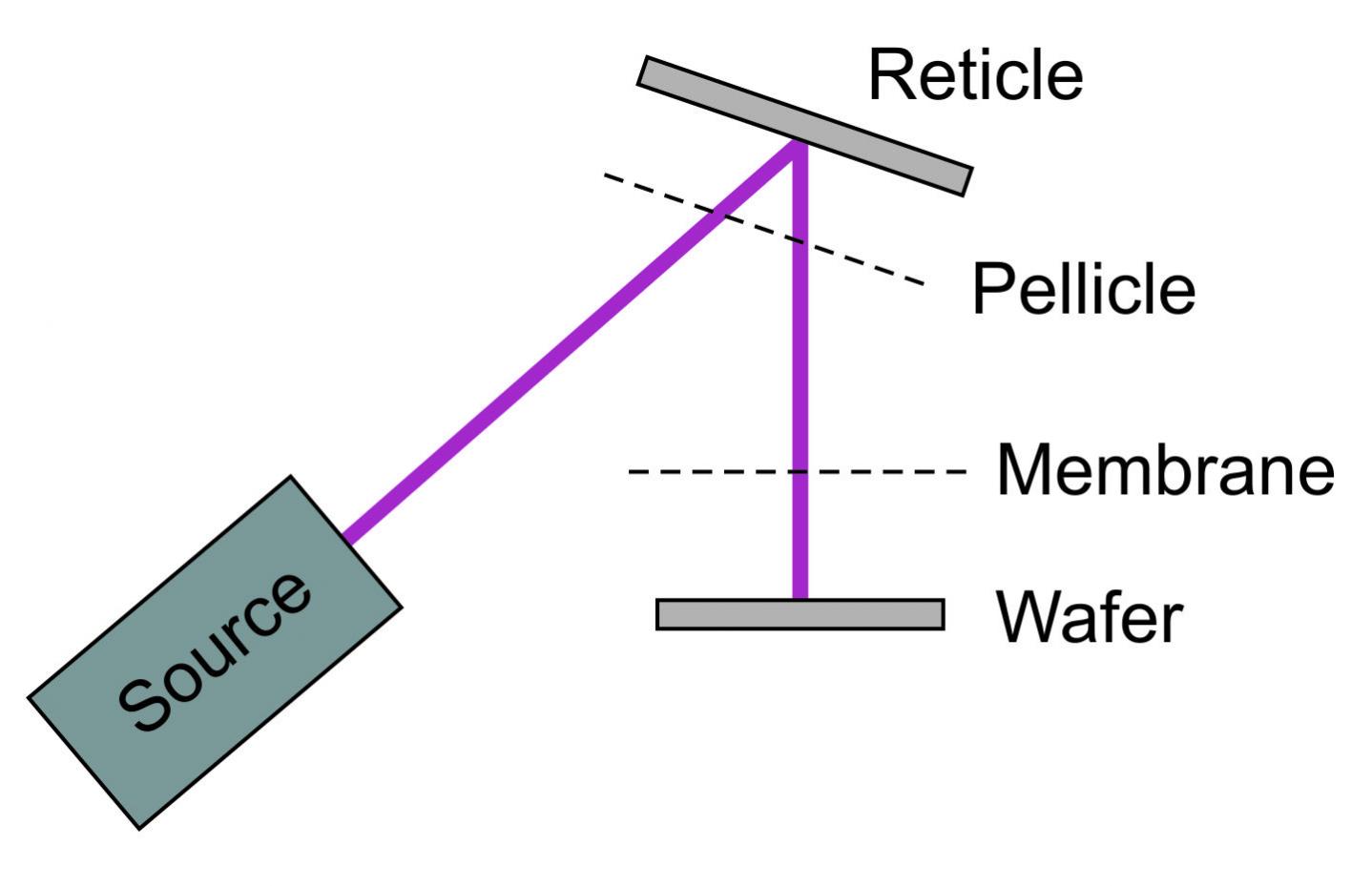

SPIE Advanced Lithography 2018 – ASML Update on EUV

At the SPIE Advanced Lithography Conference in February ASML gave an update on their EUV systems, in this blog I will provide a summary of what they presented. I have also written about my impressions on EUV for the overall conference here.… Read More

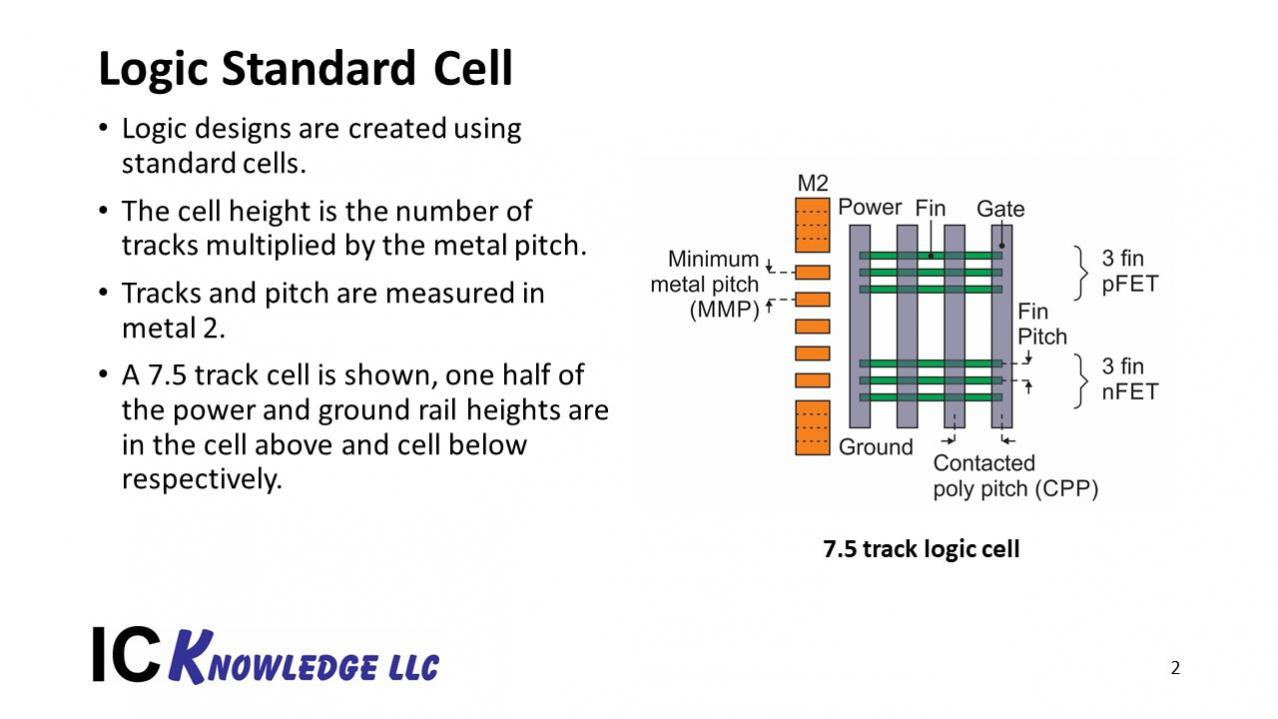

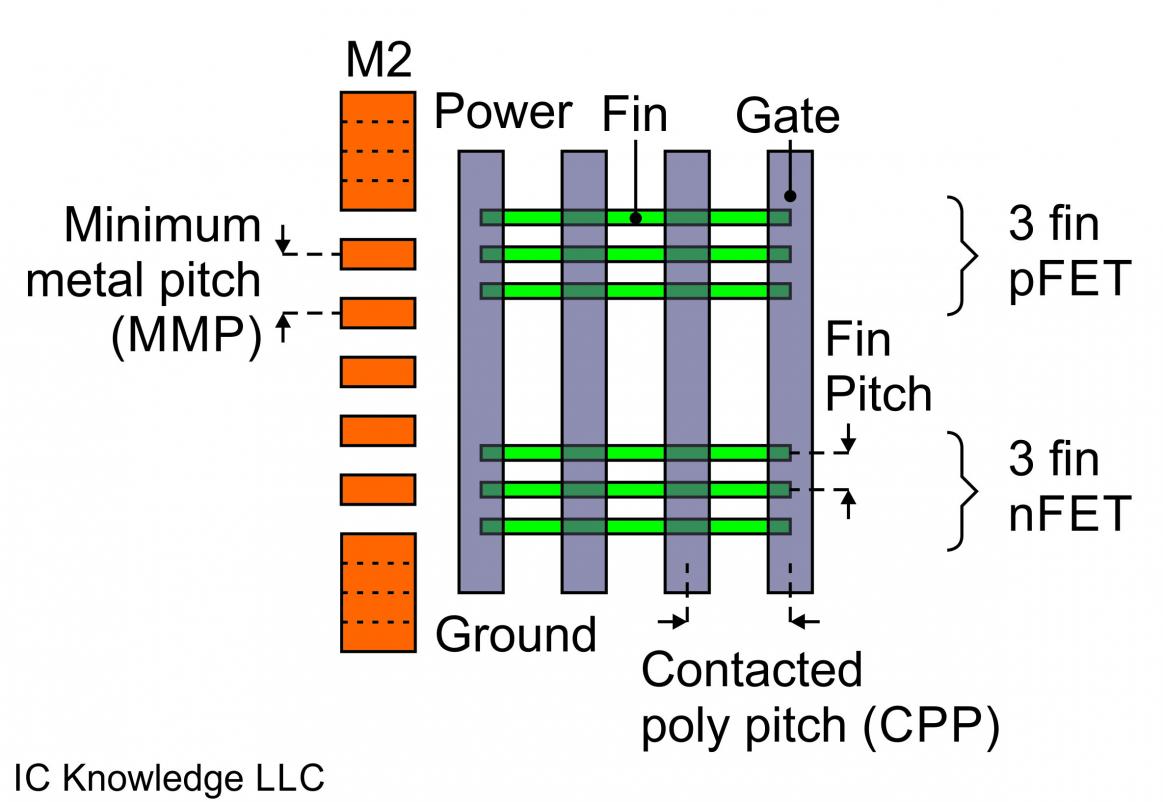

Leading Edge Logic Landscape 2018

The most viewed blogs I write for SemiWiki are consistently blogs comparing the four leading edge logic producers, GLOBALFOUNDRIES (GF), Intel, Samsung (SS) and TSMC. Since the last time I compared the leading edge new data has become available and several new processes have been introduced. In this blog I will update the current… Read More

SPIE Advanced Lithography 2018 – EUV Status

This year the Advanced Lithography Conference felt very different to me than the last couple of years. I think it was Chris Mack who proclaimed it the year of Stochastics. EUV has dominated the conference for the last several years but in the past the conversation has been mostly centered on the systems, system power and uptime.

I … Read More

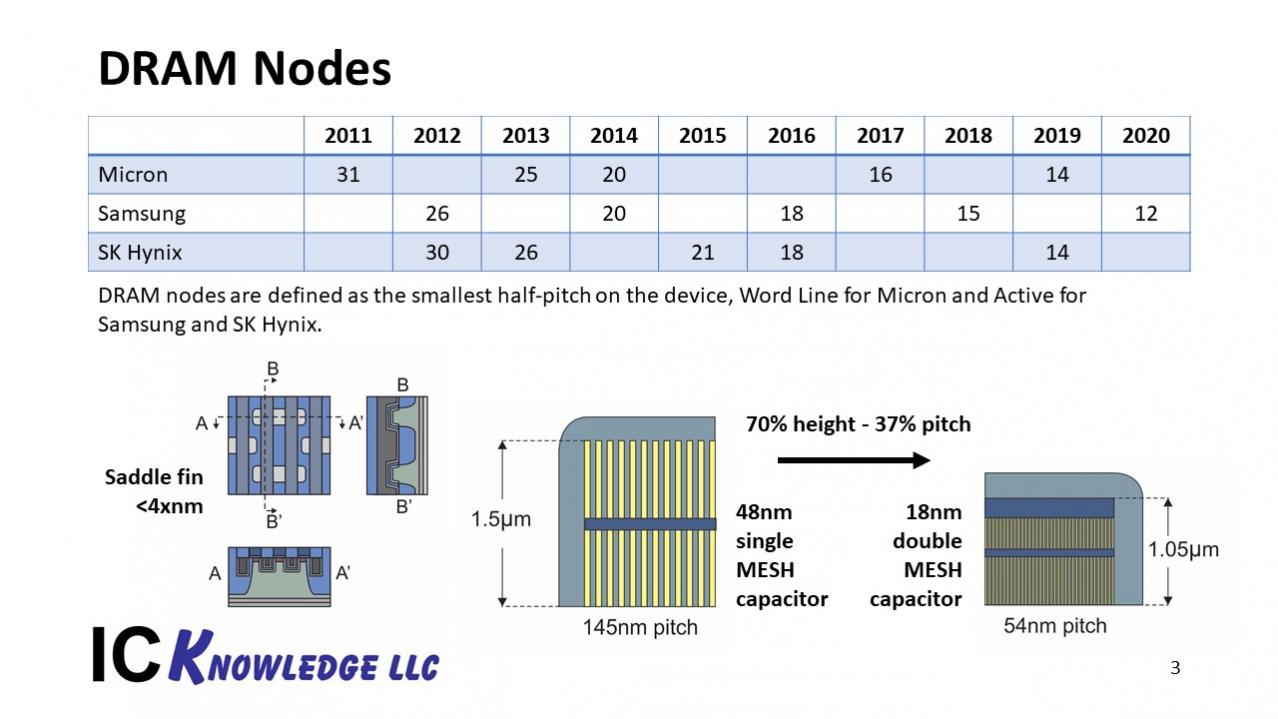

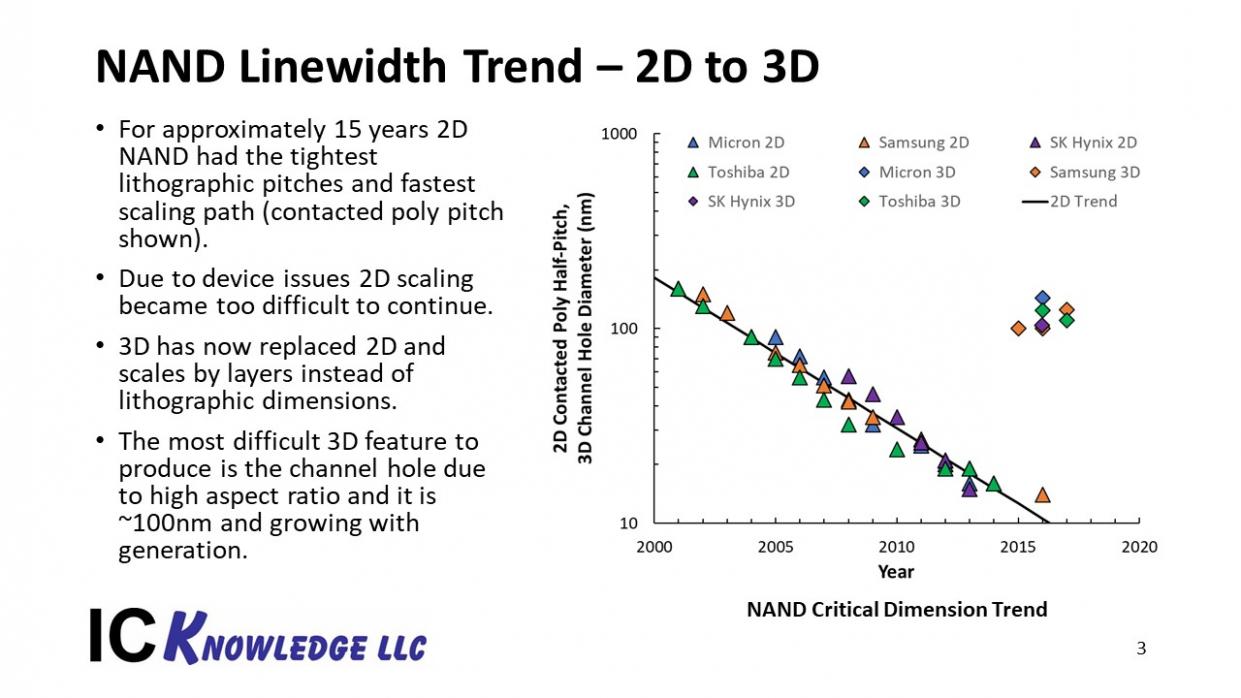

LithoVision 2018 The Evolving Semiconductor Technology Landscape and What it Means for Lithography

I was invited to present at Nikon’s LithoVision event held the day before the SPIE Advanced Lithography Conference in San Jose. The following is a write up of the talk I gave. In this talk I discuss the three main segments in the semiconductor industry, NAND, DRAM and Logic and how technology transitions will affect lithography.… Read More

IEDM 2017 – Leti Gate-All-Around Stacked-Nanowires

At IEDM in December I had a chance to interview Thomas Ernst about the paper “Performance and Design Considerations for Gate-All-around Stacked-NanoWires FETs” by Leti and STMicroelectonics.

Leti published the first stacked nanowire in 2006, it was very new then, now stacked nanowire/nanosheets are starting… Read More

IEDM 2017 – Controlling Threshold Voltage with Work Function Metals

As I have said many times, IEDM is one of the premier conferences for semiconductor technology. On Sunday before the formal conference started I took the “Boosting Performance, Ensuring Reliability, Managing Variation in sub-5nm CMOS” short course. The second module in the course was “Multi-Vt Engineering… Read More

ISS 2018 – The Impact of EUV on the Semiconductor Supply Chain

I was invited to give a talk at the ISS conference on the Impact of EUV on the Semiconductor Supply Chain. The ISS conference is an annual gathering of semiconductor executives to review technology and global trends. In this article I will walk through my presentation and conclusions.… Read More

An AI-Native Architecture That Eliminates GPU Inefficiencies