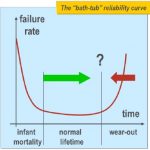

With the increase of transistors per unit area, high density interconnects and manufacturing variability at lower nodes, the electronic devices have become more vulnerable to failures. The devices that operate under extreme conditions such as automotive devices that operate at high temperatures need to be robust enough to… Read More

Author: Pawan Fangaria

Predicting Lifetime of Analog ICs

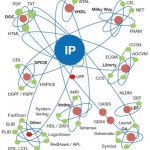

An Universe of Formats for IP Validation

Although I knew about Crossfire’s capabilities for signing off quality of an IP before its integration into an SoC, there was much more to learn about this tool when I visited Fractal Technologies booth during this DAC. The complexity handled by this tool to qualify any type of IP for its integration into an SoC can be imagined by the… Read More

Can FD-SOI Change the Rule of Game?

It appears so. Why there is so much rush towards FD-SOI in recent days? Before talking about the game, let me reflect a bit on the FD-SOI technology first. The FD-SOI at 28nm claims to be the most power-efficient and lesser cost technology compared to any other technology available at that node. There are many other advantages from… Read More

New Tool Suite to Accelerate SoC Integration

Today, an SoC is seen in the context of an optimized assembly of IPs; it’s no more a single monolithic chip design. It’s very common to see an ARM processor IP along with an interconnect IP, a memory IP, and couple of buses and interfaces IP in an SoC. Although the SoC seems to be an integrated collection of IPs, it can be very complex and… Read More

Eyes Meet Innovations at DAC

It gives me a very nice, somewhat nostalgic, feeling after attending the 52[SUP]nd[/SUP] DAC. There was a period during my final academic year in 1990 and my first job when I used to search through good technical papers in DAC proceedings and try implementing those concepts in my project work. In general, representation from ‘R&D… Read More

EDA Acquisition to Drive SoC realization

A week ago I was reading an article written by Daniel Nenni where he emphasised about semiconductor acquisitions to fuel innovation. We would see that in a larger space, not only in semiconductor and FPGA manufacturing companies (e.g. Intel and Altera) but also in the whole semiconductor ecosystem. If we see it from technical perspective,… Read More

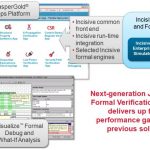

Next Generation Formal Technology to Boost Verification

With growing complexities and sizes of SoCs, verification has become a key challenge for design closure. There isn’t a single methodology that can provide complete verification closure for an SoC. Moreover creation of verification environment including hardware, software, testbench and testcases requires significant … Read More

A Robust Lint Methodology Ensures Faster Design Closure

With the increase in SoC designs’ sizes and complexities, the verification continuum has grown larger to an extent that the strategies for design convergence need to be applied from the very beginning of the design flow. Often designers are stuck with never ending iterations between RTL, gate and transistor levels at different… Read More

Changing Trends at the Top of Semicon Space

As we have moved down from a CAGR of ~9% over last three decades to a CAGR of ~5% in the current decade, it’s time to check the realities. It can be definitely argued that a 5% of CAGR over a solid base of ~$378 billion should be considered good enough. In my view that’s the sign of maturity in the semiconductor market. At the same time we are… Read More

SITRI and Coventor Partner to Scale Up MEMS in China

When it comes to wearable technology and the rapidly emerging world of IoT, sensors and MEMS are on the frontlines. They collect and transfer raw data such as pressure, temperature and motion and process it with algorithms critical to making sure the right information gets to humans and/or machines so the right reaction is enabled.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center