You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

At DVCon on Thursday March 1st (St David’s day for any Welsh readers) Jasper is sponsoring lunch from 12pm to 1.30pm. It will take place in the Cascade/Sierra ballrooms.

During lunch there will be a panel discussion Formal Verification from Users’ Perspectives with real users no how they mitigate risk in their designs… Read More

3D Standardsby Paul McLellan on 02-01-2012 at 5:06 pmCategories: Ansys, Inc., EDA

At DesignCon this week there was a panel on 3D standards organized by Si2. I also talked to Aveek Sarkar of Apache (a subsidiary of Ansys) who is one of the founding member companies of the Si2 Open3D Technical Advisory Board (TAB), along with Atrenta, Cadence, Fraunhofer Institute, Global Foundries, Intel, Invarian, Mentor, Qualcomm,… Read More

Next week there are two Apache, a subsidiary of Ansys, events. At DesignCon there are a couple of workshops on chip-package-system (CPS). In addition to Apache themselves, each of the two workshops has a number of representatives of leading edge companies doing semiconductor design. I already blogged about this in more detail… Read More

Well it looks like everyone (including me) was way too conservative about Apple’s iPhone sales last quarter. Analysts were expecting Apple to sell 30M iPhones and 13M iPads. In fact they sold 37M iPhones, almost a quarter more than expected, and over 15M iPads. In fact Apple sold more iPads than HP, the largest PC manufacturer,… Read More

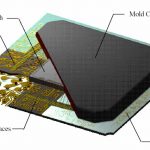

3D and 2.5D (silicon interposer) designs create new challenges for EDA. Not all of them are in the most obvious areas. Mentor has an interesting presentation on what is required for verification and testing of these types of designs. Obviously it is somewhat Mentor-centric but in laying out the challenges it is pretty much agnostic.… Read More

“Before we acquire great power we must acquire wisdom to use it well”

Ralph Waldo Emerson

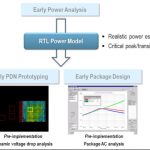

Making good architectural decisions for controlling power consumption and ensuring power integrity requires a good analysis of the current requirements and how they vary. Low power designs, and today there really aren’t… Read More

Apple’s iPhone did well in Q4 according to Neilsen who polled recent buyers of smartphones. Of people who had purchased a smartphone in the previous 3 months (roughly Q4) 44.5% chose an iPhone (up from 25.1% in October, roughly Q3). But Android retained the lead with a 46.9% share, down from 61.6% in October. How many phones… Read More

For the next few days Atrenta is running a series of 30 minute live webinars to discuss the new solutions and approaches that are required to improve the way SoC designs are created and modified.

The webinars are at the following times:

- Jan 17th, 7-7.30am PST (sorry you missed that one)

- January 18th 7.30-8pm PST (and January 19th in

…

Read More

Chips, packages and circuit boards (systems, hence CPS) used to be three separate domains with their own tools that barely interacted at all. If you were lucky, reassigning a pin on a package wouldn’t have to be done manually in all 3 places. But now, from a signal integrity, noise, power point of view these three domains must… Read More

Note that there are several DAC deadlines coming up in the next couple of weeks.

The deadline for user track submissions is January 17th (next Tuesday). Submission requires an extended abstract. See here for details.

The deadline for DAC workshops is January 19th (next Thursday). A proposal is required. See here for details.

The… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era