Yesterday at the Globalpress electronic summit Andrew gave an overview of the Apache product line, carefully avoiding saying anything he cannot due to the filing of Apache’s S-1. From a financial point of view the company has had 8 years of consecutive growth, is profitable since 2008, and has no debt. During 2010 when the… Read More

Author: Paul McLellan

Process Design Kits: PDKs, iPDKs, openPDKs

One of the first things that needs to be created when bringing up a new process is the Process Design Kit, or PDK. Years ago, back when I was running the custom IC business line at Cadence, we had a dominant position with the Virtuoso layout editor and so creating a PDK really meant creating a Virtuoso PDK, and it was a fairly straightforward… Read More

RTL Power Analysis and Verification

“Power is the new timing” has almost become a cliché. There are a number of reasons for this, not least that increasingly it is power rather than anything else that caps the performance that a given system can deliver. Power is obviously very important in portable applications such as smartphones because it shows through directly… Read More

Apache files S-1

Apache Design Solutions today filed their S-1 with the SEC in preparation for its initial public offering (IPO). This is a big deal since there hasn’t been an IPO of an EDA company for may years (Magma was the last 10 years ago). As a private company they have not had to reveal their financials until now.

It turns out that they did… Read More

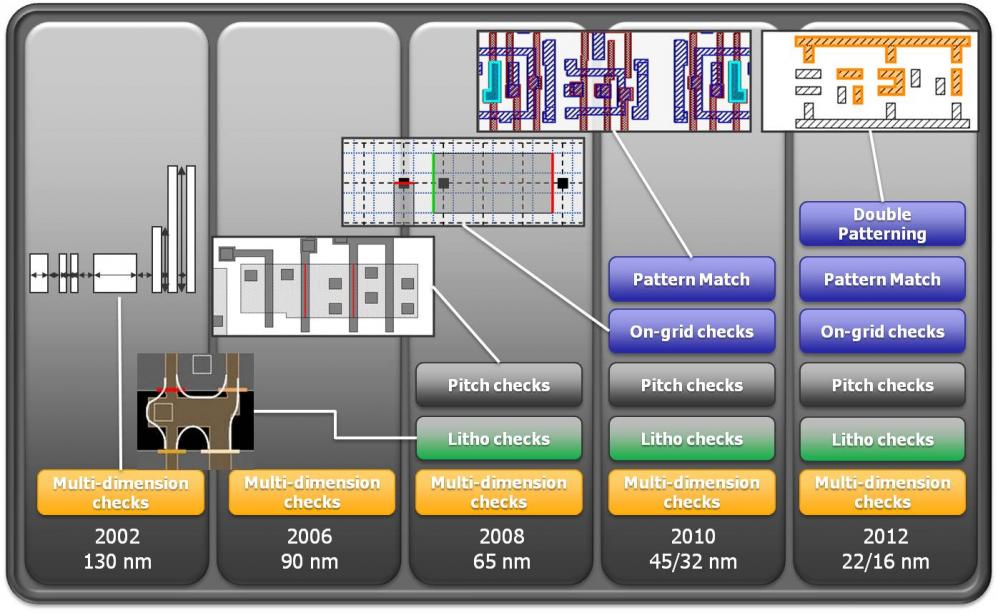

Checking AMS design rules instantly

With each process generation, the design rules get more and more complex. One datapoint: there are twice as many checks at 28nm as there are at 90nm. In fact, the complexity of the rules is outpacing the ability to describe them using the simplified approaches used in the DRCs built-into layout editors or formats like LEF.

Worse still,… Read More

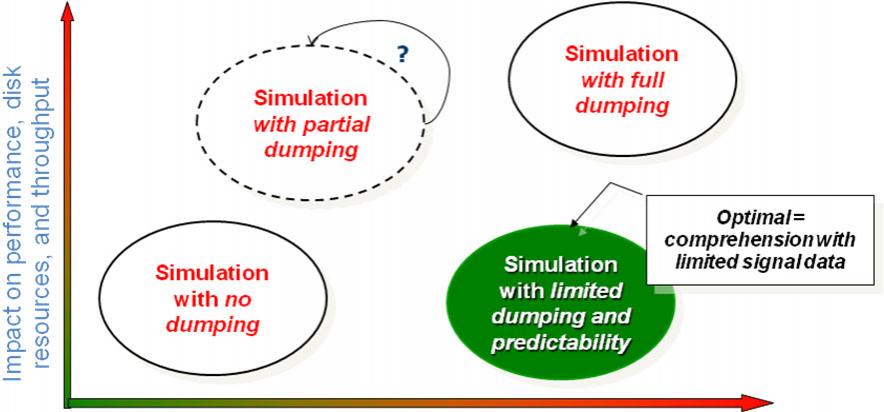

Essential signal data and Siloti

One of the challenges with verifying today’s large chips is deciding which signals to record during simulation so that you can work out the root cause when you detect something anomalous in the results. If you record too few signals, then you risk having to re-run the entire simulation when you omitted to record a signal that… Read More

Clock Domain Crossing, a potted history

Yesterday I talked to Shaker Sarwary, the senior product director for Atrenta’s clock-domain crossing (CDC) product SpyGlass-CDC. I asked him how it came about. The product was originally started nearly 8 years ago, around the time Atrenta itself got going. Shaker got involved about 5 years ago.

Originally this was a small… Read More

Synopsys at Goldman Sachs Technology Conference

Aart de Geus was interviewed at the Goldman Sachs Technology Conference last week. Here is some of what he said. Strong Q1, good Q2 outlook, on-track for 2011 guidance. Strong rebound in Far East, Europe mixed, North America good. 80% revenue for year booked by start of year, 90% revenue for a quarter already booked at start of quarter.… Read More

Clock Domain Crossing (CDC) Verification

Multiple, independent clocks are quintessential in SoCs and other complex ASICs today. In some cases, such as in large communications processors, clock domains may number in the hundreds. Clock domain crossings pose a growing challenge to chip designers, and constitute a major source of design errors–errors that can… Read More

EDA and Wall Street

Good news in a way: Merrill Lynch (or Bank of America Merrill Lynch as I suppose we have to get used to calling them) have re-started coverage of EDA with a 20 page report on the industry, much of which is spent on explaining how the industry segments out and who is strong in which segments, stuff that most people reading this site already… Read More

Elon Musk Given CHIPS Act & AI Oversight – Mulls Relocation of Taiwanese Fabs