If you are involved in designing systems that process data, you’re going to want to attend this webinar. Practically speaking, this should include a large percentage of the SemiWiki readership. Since data is the new oil there are a lot of applications drawn to data and information processing. Before we explore this webinar, let’s… Read More

Author: Mike Gianfagna

Silicon Catalyst is Bringing Its Unique Startup Platform to the UK

Silicon Catalyst is a unique startup incubator / accelerator that focuses exclusively on accelerating solutions in silicon (including chips, IP, MEMS & sensors). The organization has an extensive support infrastructure that includes preferred access to IP, design tools, business infrastructure and fab/assembly. … Read More

Your IP Portfolio is Probably Leaking. What Can You Do About It?

This topic is inspired by a presentation at last year’s DAC presented by Methodics, now part of Perforce. The issues raised by the original presentation are still quite relevant in the current business climate. IP leakage is something everyone should consider as part of their normal business operations. Your design IP really … Read More

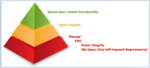

Samtec Keynote – Power Integrity is the New Black Magic

The Signal Integrity Journal recently held a half day Electronic Systems SI/PI Forum that included presentations from industry leaders covering key design topics for signal integrity and power integrity engineers. The event was sponsored by Cadence. The keynote for the event was presented by Istvan Novak, principal signal… Read More

The Juggernaut Continues as ESD Alliance Reports Record Revenue Growth for Q4 2020

Apologies for the slightly hyperbolic title of this post. Webster defines Juggernaut as “a massive inexorable force, campaign, movement, or object that crushes whatever is in its path.” Marvel Comic fans will recall the term also refers to a superhero nemesis. But I digress. The ESD Alliance recently announced its Q4 2020 Electronic… Read More

Webinar: Annapurna Labs and Altair Team up for Rapid Chip Design in the Cloud

This is a story of strategic recursion. Yes, a fancy term. I just made up. If you’re not into algorithm development you can Google recursion, but the simple explanation is we’re talking about using the cloud to design the cloud. The story begins with Annapurna Labs, a fabless chip company focused on bringing innovation to cloud infrastructure,… Read More

Flex Logix Closes $55M in Series D Financing and Accelerates AI Inference and eFPGA Adoption

Flex Logix is a unique company. It is one of the few that supplies both FPGA and embedded FPGA technology based on a proprietary programmable interconnect that uses half the transistors and half the metal layers of traditional FPGA interconnect. Their architecture provides some rather significant advantages. I wrote about their… Read More

Sondrel Explains One of the Secrets of Its Success – NoC Design

Sondrel is an interesting and unique company. They are a supplier of turnkey services from system to silicon supply. So far, not that unique as there are a lot of companies with this mission. What is unique is their focus on complex designs. The company takes on the design of chips that would need teams of engineers working for a year… Read More

Webinar: Samtec Teams with Otava and Avnet to Tame mmWave Design

mmWave design has traditionally been a boutique technology used in satellite and defense applications. Lately that’s changing. It turns out the complex, high frequency capabilities of mmWave technology are a key enabler for the 5G wireless networks being deployed today. I discussed some of this backstory in a recent post about… Read More

Perforce Embedded DevOps Summit 2021 and the Path to Secure Collaboration on the Cloud

Perforce recently held their virtual Embedded DevOps Summit. There was a lot of great presentations across many disciplines. Of particular interest to me, and likely to the SemiWiki readership as well, was a presentation by Warren Savage entitled Secure Collaboration on a Cloud-based Chip Design Environment. I’ll provide … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era