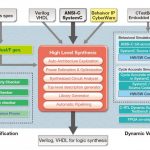

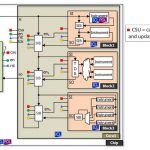

Perhaps no area in EDA has been as enigmatic as high-level synthesis (HLS). At nearly every industry event, some new-fangled tool always seems to be tabbed as the next big thing by some analyst or pundit. In a twist, the latest news is on one of the oldest tools – CybeWorkBench.… Read More

Author: Don Dingee

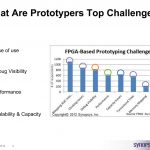

More to the story than bigger FPGA-based prototyping

Still not convinced on the value of FPGA-based prototyping systems, or using older technology? I’ve been trying to find the story beyond just bigger, badder FPGAs in a box that you pour RTL into – and found some hints in a webinar on the Synopsys HAPS-70 from earlier this year.… Read More

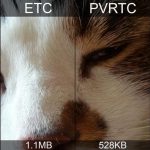

Compressing OpenGL ES textures

The 80s called, and they want lazy programming back. Remember “Mr. Mom”? Michael Keaton is talking about rewiring the house, and Martin Mull asks if he’s going to use all 220V, and Keaton responds “Yeah, 220, 221, whatever it takes.” Not knowing what’s inside can make you look silly.

Such is the case with OpenGL ES. Taking a look at … Read More

How many consortia does POWER need to succeed?

Sometimes press releases just make me scratch my head. Today’s example comes from IBM: after tying PowerPC and Power.org in knots for almost 20 years with rules and restrictive licensing, IBM breaks ranks and sets up ANOTHER consortium with different players.… Read More

Scan the horizon, P1687 takes us higher

The tech standards cycle almost always goes like this: Problems or limits develop with the existing way of doing things. Innovators attempt to engineer solutions, usually many of them. Chaos ensues when customers figure out nothing new works with anything else. Competitors sit down and agree on a specification where things work… Read More

Constrain all you want, we’ll solve more

EDA tool development is always pushing the boundaries, driven in part by bigger, faster chips and more complex IP. For several years now, the trend has been developing tools that spot problems faster without waiting for the “big bang” synthesis result that takes hours and hours. Vendors, with help from customers, are tuning tools… Read More

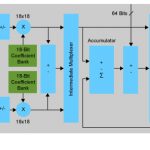

The fixed and the finite: QoR in FPGAs

There is an intriguingly amorphous term in FPGA design circles lately: Quality of Results, or QoR. Fitting a design in an FPGA is just the start – is a design optimal in real estate, throughput, power consumption, and IP reuse? Paradoxically, as FPGAs get bigger and take on bigger signal processing problems, QoR has become a larger… Read More

Workload-tuned cores seeing greater interest

Is it possible to design a processor with very high performance and low power consumption? To answer that, embedded illuminati are now focusing on designs tuned to specific workloads – creating a tailored processor that does a few things very efficiently, with nothing extra.… Read More

So, where are all the EMBEDDED guys?

Roaming the aisles at #50DAC the past week left me with one unmistakable impression: there were two shows going on at the same time. Oh, we were all packed into one space together at the Austin Convention Center and neighboring hotels. But we weren’t quite all speaking the same language – yet.… Read More

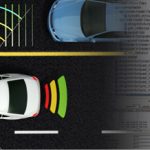

10 years, 100,000 miles, or <1 DPM

Auto makers have historically been accused of things like planned obsolescence – redesigning parts to make repairs painfully or even prohibitively expensive – and the “warranty time-bomb”, where major systems seem to fail about a week after the warranty expires. Optimists would chalk both those up to relentless innovation,… Read More

Solving the EDA tool fragmentation crisis