Flip on the TV, and a car commercial is bound to pop up shortly touting one of two technological aspects. One is center stack integration of smartphone-style applications. The other is advanced driver assistance systems (ADAS) featuring cameras, radar, and other sensors helping cars … Read More

Author: Don Dingee

Sidense overlays OTP on TSMC 16nm FinFET

Process shrinks, which have served us well for most of the Moore’s Law journey, are reaching their limits. For switching transistors, the biggest problems of leakage current and gate oxide vulnerability in planar MOSFETs have led the industry to new 3D microstructures such as FinFET. For non-volatile memory, the problem is generally… Read More

New details on Altera network-on-FPGA

Advantages to using NoCs in SoC design are well documented: reduced routing congestion, better performance than crossbars, improved optimization and reuse of IP, strategies for system power management, and so on. What happens when NoCs move into FPGAs, or more accurately the SoC variant combining ARM cores with programmable… Read More

Opting for ARM software scalability

Behind much of the success of ARM architecture is a scalable software model, where in theory the same code runs on the smallest member of the family to the largest. In practice, there are profiles, and a variety of hardware execution units, and resource constraints in low power scenarios that enter the picture. As a result, operating… Read More

Secure at any IoT deed

In his classic book “Unsafe at Any Speed”, Ralph Nader assailed the auto industry and their approach to styling and cost efficiency at the expense of safety during the 1960s. He squared up on perceived defects in the Chevrolet Corvair, but extended his view to wider issues such as tire inflation ratings favoring passenger comfort… Read More

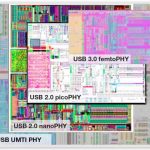

USB 3.0 IP on FinFET may stop port pinching

Sometimes a standard is a victim of its own success, at least for a while as the economics catch up to the technology. When a standard like USB 3.0 is announced, with a substantial performance increase over USB 2.0, some of the use cases come on board right away. Others, where vendors enjoy a decent ROI with good-enough performance,… Read More

Another debug view in the UVM Toolbox

One of the biggest endearing qualities of a debug environment for any type of coding is availability of multiple ways to accomplish a task. Whether the preference is keyboard shortcuts, mouse left-click drill-down and right-click pull-down menus, source code view, hierarchical class view, or graphical relationship view, … Read More

IBM thinks neural nets in chip with 4K cores

Neural networks have been the darlings of researchers since the 1940s, but have eluded practical hardware implementations on all but a small scale, or an enormous one given how many processing elements and interconnects are needed. To make significant brain-like decisions, one needs at least several thousand fairly capable… Read More

Then, Python walked in for verification

Go ahead – type “open source” into the SemiWiki search box. Lots of recent articles on the IoT, not so many on EDA tools. Change takes a while. It has only been about five years since the Big Three plus Aldec sat down at the same table to work on UVM. Since then, Aldec has also gotten behind OS-VVM, and is now linked to a relatively new open… Read More

Wipe that smile off your device

Privacy is a tough enough question when using a device – but what about when we’re done with it? In a world of two year service agreements with device upgrades and things being attached to long-life property like cars and homes, your data could fall into the hands of the next owner way too easily.

“Oh, it’s OK, I wiped the phone with a factory… Read More

Solving the EDA tool fragmentation crisis